Hello all,

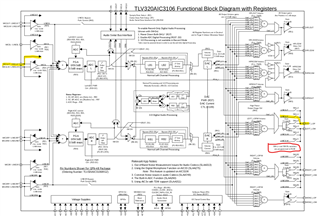

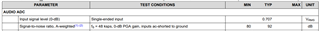

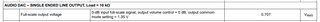

We are using a TLV320AIC3106 in an scenario where we adjust the levels of a microphone signal received in LINE1LP pin (in signle-ended mode) and we output it through LEFT_LOP.

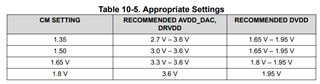

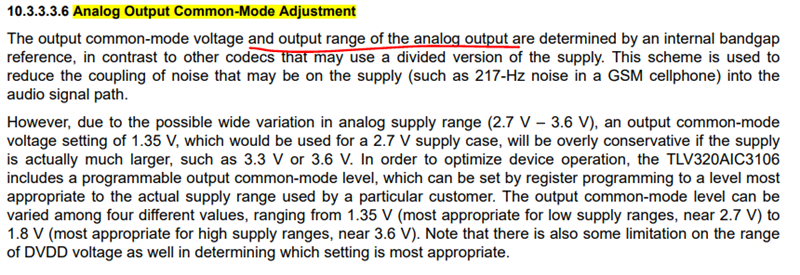

We have recently realized the signals outputed by LEFT_LOP are saturating at slightly less than 2.7V Vpk-pk. After reviewing the datasheet we have detected a setting we did not noticed before: the "Analog Output Common-Mode Adjustment". After navigating through the datasheet we ended discovering "Page 0 / Register 40: High Power Output Stage Control Register" and after that we modify the bits D7-D6 from 00 to 10 since we are powering the IC with 3V3 for IOVDD / DRVDD and 1V8 for DVDD.

We checked again LEFT_LOP output voltage saturation level and... unfortunately nothing changed, output still saturating at slightly less than 2.7V Vpk-pk so it seems we are missing something.

Right now we have the following questions:

- Output Common-Mode adjustment works as we expect? I mean:

- It affects the behaviour of LEFT_LOP output both in single-ended and differential mode

- If D7-D6 = 00, then LEFT_LOP output signal will saturate at 2V7.

- If D7-D6 = 10, then LEFT_LOP output signal will saturate at 3V3.

- "Page 0 / Register 40: High Power Output Stage Control Register" is the right register to modify not only HPLOUT but also LEFT_LOP outputs Output Common-Mode adjustment. I ask this because the name of the register is somewhat misleading.

- Can "Page 0 / Register 42: Output Driver Pop Reduction Register" bit D1 be related with this topic?

- If with our current configuration (D7-D6 = 00) output signal saturates at aroung 2.4V instead of 2.7V (Vpk-pk). Could this mean that we are limiting the output voltage in a different way than with Analog Output Common-Mode Adjustment? If the answer is yes then:

- If we are unintentionally limiting this output voltage range to let say 2.4V, Would D7-D6 bits value affect? or it wouldn't matter to have it configured to 2V7 or 3V3 since the signal is limited earlier to 2V4?

- What registers could also affect the output voltage range?

Do you have any guidance of what can we doing wrong? Please not input signal is around 2.3V (Vpk-pk) and is NOT saturated.

Thank you very much in advance!

Best regards,