Hello

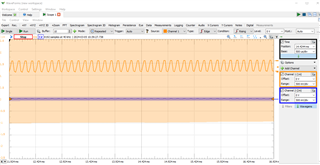

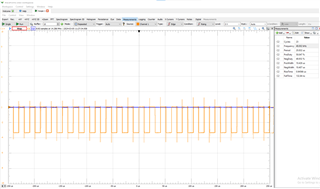

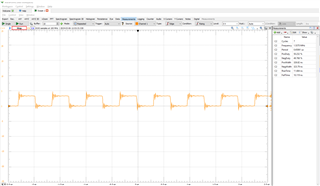

I have been trying to get our AMP to work with our design, but to no avail. I started with testing on the development board, and got both an I2C driver and an I2S driver up and running where I could play audio just fine. But for some reason I cannot get it to work with our integrated desing. It is run on an ESP32S which is the same as the one used when testing the development board.

Here is the schematic used for the TAS amp

And here is the current version of the configuration sequence

During the meta_burst section I of course read the next first hex as the address followed by the next X hex as the value to write, with X being given from {CFG_META_BURST,X}

Can anyone spot what is wrong? I read the live interrupts and there is no issues. The I2S is configured to have a sample rate of 48000, left justified, 1 channel and 16 bits per sample, and the I2C clockfrequency is