Hi all,

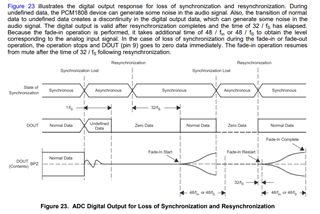

I am trying to read an analog signal using a PCM1808 and running into a very strange issue. I am feeding a sine wave (centered around 2.5v) into the chip and reading back an extremely distorted signal through the I2S interface. More confusingly, the distortion appears to be highly asymmetrical, with the "negative half" of the waveform experiencing far more distortion. Below is a screengrab of the I2S data:

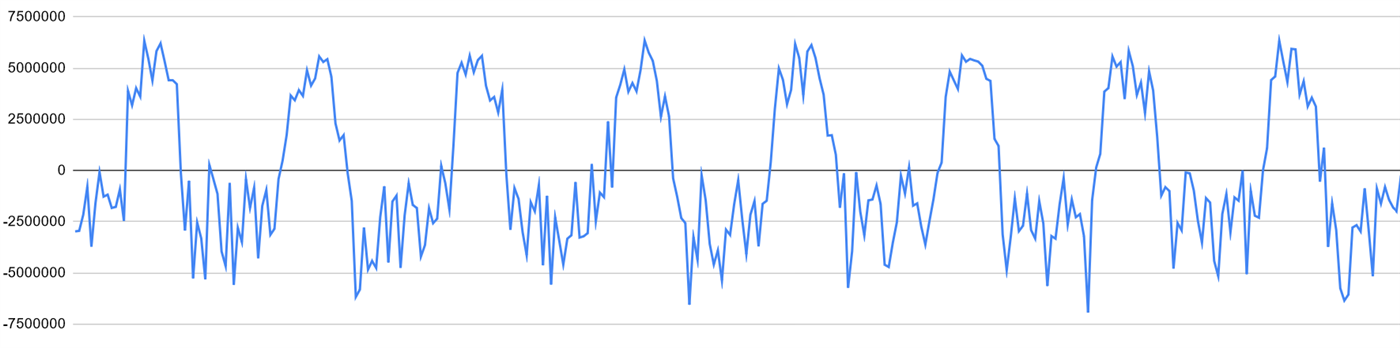

As a sanity check, here is the input signal, recorded directly at the chip. 2.5vpp 1khz.

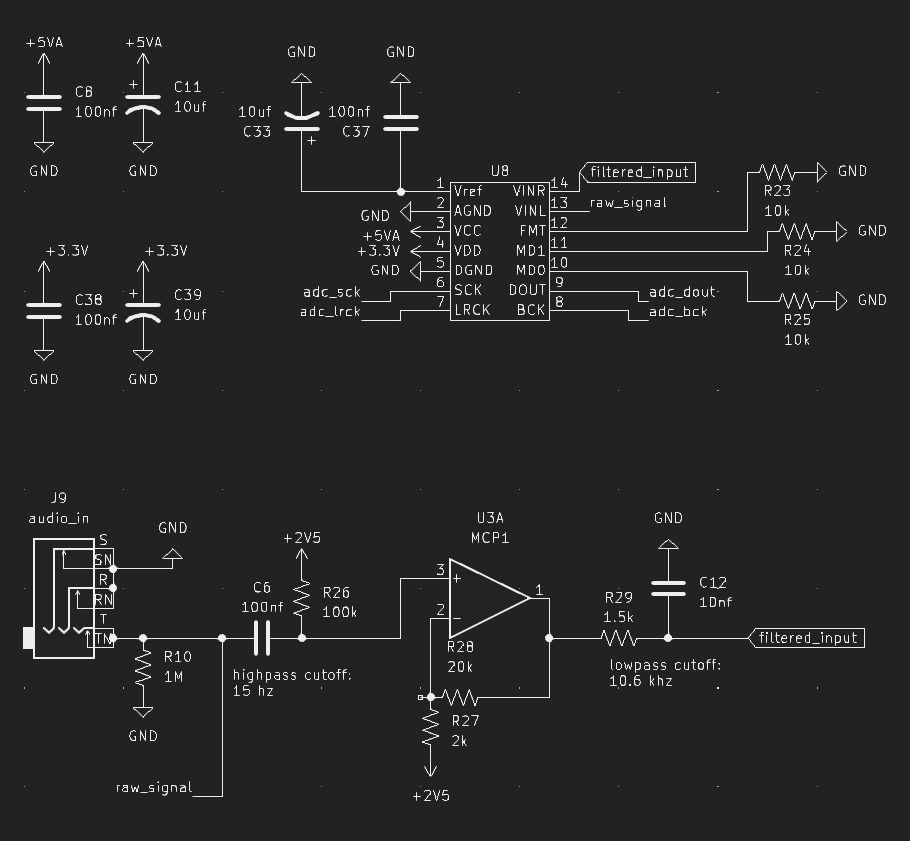

My design is essentially just the reference design, and I have verified that power / ground supplies are stable.

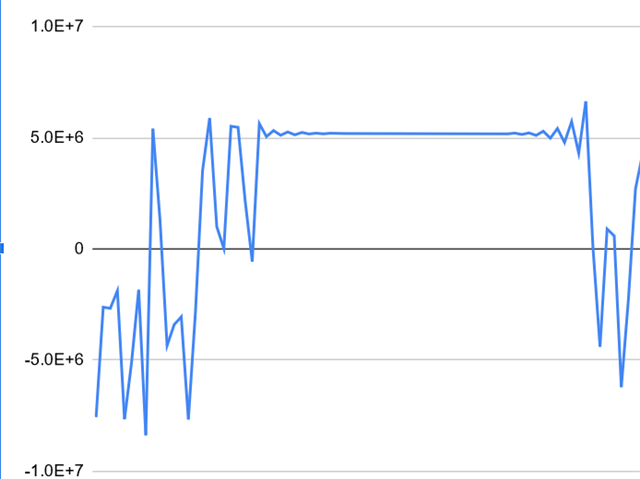

I have also noticed that at points, the input appears to "freeze" and experiences ringing. The strange thing is that this ringing seems to happen at the beginning and end of the frozen section, as if it's able to anticipate the "un-freezing", which leads me to think that something is happening internally in the chip? Below is a graph of the i2s data when being fed a slower 100hz sine wave. As you can see, it appears to freeze for ~100 samples, and rings at the beginning and end:

I really have no idea what's going on- I would almost be inclined to assume that I have a damaged part / board, except for the fact that I have two of them and they're behaving identically. If anyone has seen something like this before or can suggest anything to try, please let me know!

EDIT: Here is the relevant portion of my schematic, including input amplification. As you can see, it is nearly identical to the reference implementation. I am seeing identical behavior on both inputs (raw and 11x amplification), though the above screenshots have been from the amplified source. I've also tried adding a 0.1uf cap between the signal and chip input pin to see if that makes a difference, but that didn't solve the issue.

Thanks!