Tool/software:

Hi, Team

Our customer use TLV320ADC6140 in their project, and they meet some EMI issues.

after check, they found the issue maybe caused by the BCLK (BCLK fw is 24.576M Hz). the BCLK waveform shows that the BCLK signal waveform is distorted, and they believe it is caused by signal reflection. If the PCB is not good enough, it has the signal reflection. But as the PCB is fixed, they prefer add a cap to the BCLK to improve the signal quality.

Pls check their test as below:

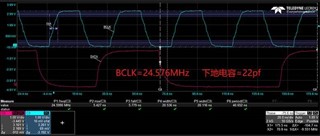

Test 1: add 22pF to the BCLK pin.

Test 2: add 47PF to the BCLK pin.

From the 22pF and 47pF cap test, we can see that the 22pF cap is better even though it has some distorted.

My customer prefer check with us for below question:

1, For 22pF can 47pF cap waveform, Do you think this waveform will affect the normal operation of ADC6140 ? pls note the waveform has some distortion, but the rise/falling time can match our datasheet.

2, What's the max capacitance loading for BCLK? ADC6140 datasheet shows (in "7.10 Timing Requirements: TDM, I2S or LJ Interface") ADC6140 I2S timing test is base on condition for cap loading is 20pF. Customer prefer to check whether 20pF is the max cap loading for BCLK?

3, do u have any others ideas to improve the BCLK performance besides optimizing the PCB?

Thanks.

G.W