Tool/software:

Hello everyone,

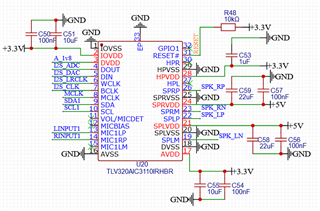

First of all, I want to let you know that I am new to hardware design, so please be gentle. Anyway, I integrated the TLV320AIC3110 into my project, based on the datasheet sample design, and the speaker output works without an issue. However, when I am recording, there is a continuous beep sound. I couldn't follow the suggested layout due to limited space, and I couldn't separate the analog ground and digital ground on my PCB. I placed all the capacitors very close to the codec, but the analog ground and digital ground are mixed.

While debugging, I thought the issue might be related to AVDD power supply noise and separated the AVDD power line from the board, but it didn't work. The system is based on Linux, and I am using kernel driver 6.6.y. I tried many things on the software side, but nothing worked. Could someone help me identify the issue?

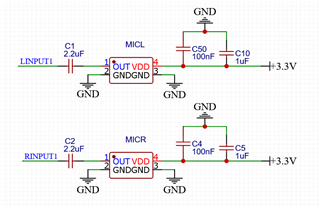

There are two analog MEMS microphones used as capture devices. I tried different mics, but nothing changed. I believe the issue is not related to the microphones.

Thank you!

Sample record in a silence room.