Tool/software:

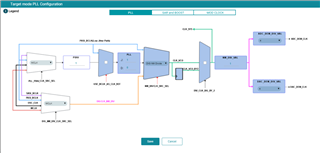

In PurePath Console 3 in the TAC5x1x-Q1 app with theTAC5212 selected, in the "Audio Serial Bus" tab under "Primary ASI Format Configuration" there is a button "Configure PLL" that opens three block diagrams GUI's that alloy you to set the PLL and clock dividers for the CODEC. Is there a guide on how to use set up the clock dividers, and is there reference material that explains what all of the divider acronyms mean.

I am trying to set up the TAC5212 to have MCLK in and it's internal PLL off, with the clock dividers set up manually. I have used the AIC3206 in the past and all the information on how to set up the clock dividers is in the application reference guide. The TAC5212 data sheet does not have information of how to manually setup the clock dividers. I am interested in having the lowest power possible while having stereo ADC for a battery operated application, so I want the PLL off to save power, if there are any premade setups in PPC3 I can try please point me to them, and/or guide material on how to set up the clock dividers.