Other Parts Discussed in Thread: TLV320ADC6140

Tool/software:

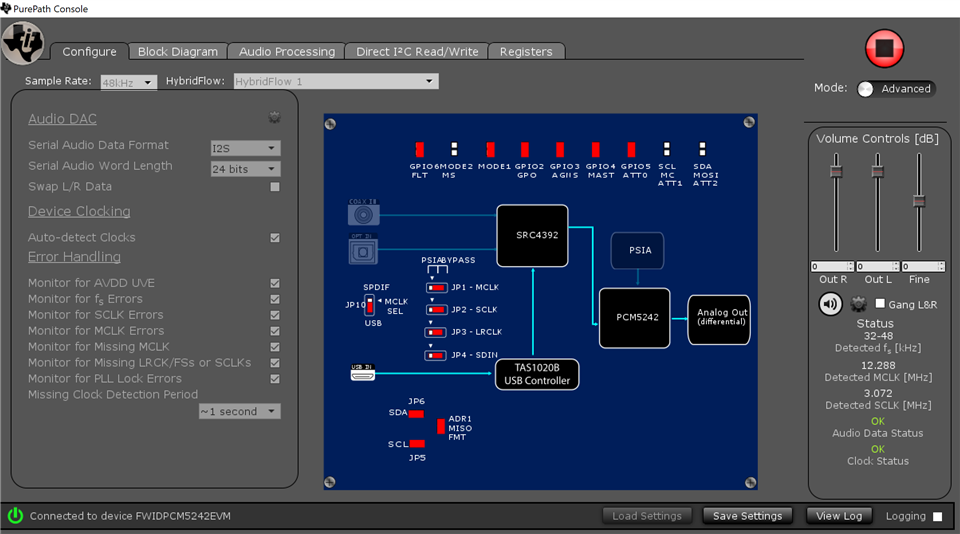

We have the following configuration:

One µController connected to 2 ADC (TLV320ADC6140) running at 48kHz and 1 DAC (PCM5242) sharing the same TDM clocks (bit clock and frame select) synchronized.

For this test config we simply would like to see an output signal as similar as possible to the input signal.

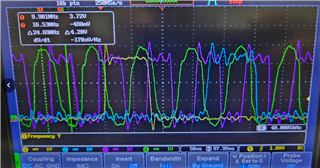

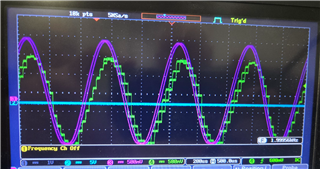

We are unable to achieve clean audio output from the DAC : if signal input frequency is low (20 Hz) it doesn't look too bad, but if we increase frequency to 200 Hz or more, DAC output is not good at all (see screenshots)

The config is :

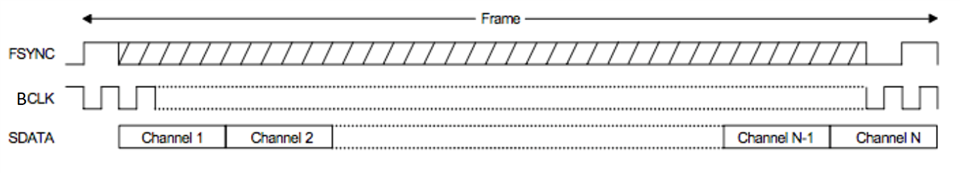

TDM 8 slots with 32 Bits data per slot (256 bits per frame)

ADC1 = master generating BCLK and FSYNC, slots 1-4

ADC2 = slave, slots 5-8

µController = two serial audio interfaces each setup as slaves. First is connected to ADC1 and ADC2 and has 8 slots. The other is connect to DAC with 8 slots too (2 first slots active)

DAC = slave, slots 1-2, single ended analog outputs. BCLK and FSYNC are connected to the signals coming from ADC1 so the DAC sees 256 bits per frame. We expect it to read the first 2x32 bits for its channels.

12.288MHZ TCXO connected to ADC MCLK and DAC SCK.

BCLK = 12.288MHZ from ADC1, data output on rising edge, valid on falling edge

FSYNC = 48 kHz over first audio bit (TDM)

Clock configuration is currently as follows: PLLCK from SCK / DACCK from SCK. Regarding OSRCK and DSPCK we are particularly puzzled...

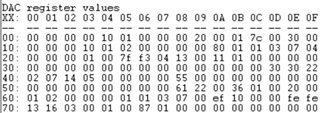

PCM5242 registers (set in this order)

0x02 : 0x10; // Standby mode

0x01 : 0x01; // reset registers

0x02 : 0x00; // Normal operation

# 20ms delay

0x04 : 0x00; // Disable pll

0x09 : 0x20; // Inverted BCK mode

0x0E : 0x30; // DAC clock source : SCK clock

0x25 : 0x1A; // Ignore SCK detection, Ignore SCK halt detection, Disable clock auto set

0x14 : 0x01; // PLL P=2 - DOCUMENTATION NOT CLEAR ON THIS

0x15 : 0x10; // PLL J=16

0x16 : 0x00; // PLL D1=0

0x17 : 0x00; // PLL D2=0

0x18 : 0x00; // PLL R=1

0x1B : 0x01; // DSP Clock Divider=2

0x1C : 0x0F; // DAC Clock Divider=16

0x1D : 0x03; // NCP Clock Divider=4

0x1E : 0x00; // OSCK Clock Divider=1

0x22 : 0x00; // 8x interpolation, single speed

0x23 : 0x04; // IDAC1

0x24 : 0x00; // IDAC2 IDAC=1024

0x28 : 0x13; // I2S Data Format=TDM/DSP, I2S Word Length=32bits

0x02 : 0x10; // Standby mode

0x02 : 0x00; // Normal operation

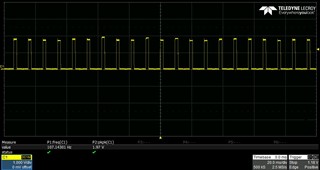

First attached screenshot corresponds to this configuration when the input signal is a 200 Hz sine wave :

Second attached screenshot is if we change this setting :

0x1E : 0x08; // OSCK Clock Divider=8

Could you please check our configuration and tell us if something is wrong ? or propose another setting for PCM5242 registers ?

We also tried to make PCM5242 work with PPC3 but it does not. We found some infos saying it works with PPC2 but seems old so probably not working anymore on Windows 11 ?