Other Parts Discussed in Thread: TLV320ADC5120, TAA5212

Tool/software:

Hi expert,

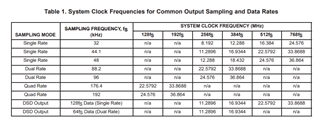

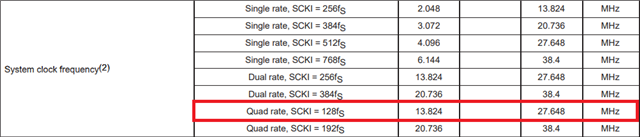

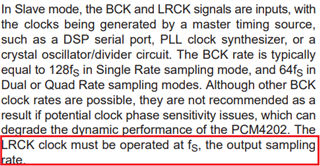

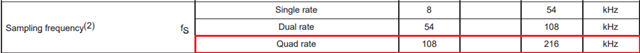

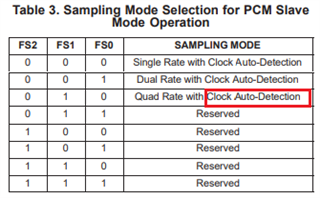

We would like to set the PCM4202 to PCM slave Mode, Quad Rate and operate the Sampling Rates at 210.9kHz.

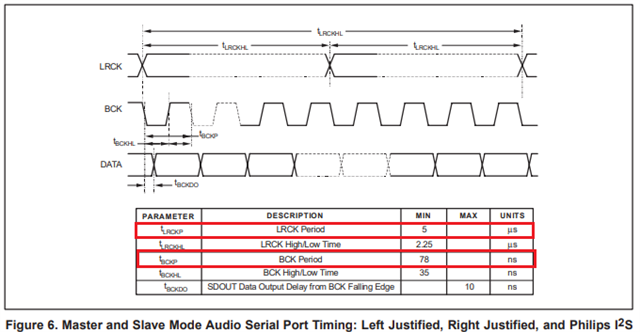

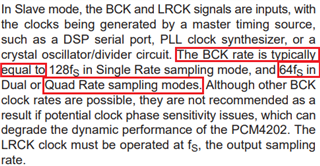

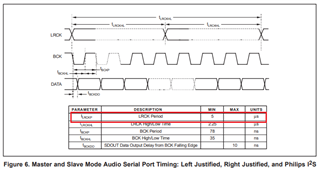

In this case, tLRCKP=4.748us(=1/210.9kHz) tBCKP=74.19ns(=tLRCKP/64). Are there any violations ?

Refer to the Datasheet

P14(,etc...) states that the maximum Sampling Rate is 216kHz, so We think 210.9kHz is within the range.

On the one hand, figure 6 states that tLRCKP=MIN 5us (tBCKP= MIN 78ns),

We are confused because the maximum Sampling Rates can be read as 200kHz(=1/5us).