Tool/software:

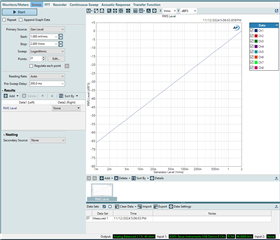

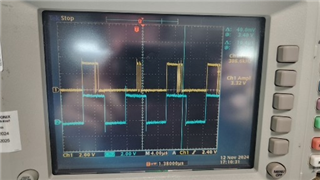

I am facing an issue where the expected resolution is not achieved when inputting a sine wave to the ADC. I would like some advice on this.

I have a major issue with my ADC design. Non-linearity check: There are large jumps in the output, particularly with the issue where the MSB 4 bits show only 0b0000 or 0b1111.Please advise.

-

Operating Mode: Slave mode

-

Power Supply Voltage: 3.3V

-

Input type : Differential input full-scale AC signal voltage

-

Output Length: 24-bit

-

Data Format: Left-justified (LJ)

-

Polarity: Unipolar

-

Reference Voltage (Vref): 2.75V

# Differential 1-channel : INP1/INM1 - Ch1 # FSYNC = 96 kHz (Output Data Sample Rate), BCLK = 6 MHz (BCLK/FSYNC = 64) ################################################################ # # # Power up IOVDD and AVDD power supplies keeping SHDNZ pin voltage LOW # Wait for IOVDD and AVDD power supplies to settle to steady state operating voltage range. # Release SHDNZ to HIGH. # Wait for 1ms. # # Wake-up device by I2C write into P0_R2 using internal AREG w 98 02 81 # # set LJ-Mode, 24 bits word length w 98 07 A0 # # Enable Line input, Typical 10-kΩ input impedance w 98 3C 84 # # Enable Input Ch-1 I2C write into P0_R115 w 98 73 80 # # Enable ASI Output Ch-1 to Ch-4 slots by I2C write into P0_R116 w 98 74 80 # # Power-up ADC and PLL by I2C write into P0_R117 w 98 75 60 # # Apply FSYNC = 96 kHz kHz and BCLK = 6 MHz MHz and # Start recording data by host on ASI bus with LJ protocol 24-bits channel wordlength