Tool/software:

Hi Teams,

The customer is using TPA3255 amplifier chips for subwoofers (PBTL mode). Currently, there are about 1500 units produced, and 2pcs of amplifier chips have been burned out and the damage is basically the same. The cause is being analyzed.

May I ask if there is any information about the pressure specifications that the chip can withstand when making heat sinks and the allowable PCB board deformation.

The customer's amplifier power supply uses PVDD=52V. When playing dynamic music, the maximum voltage measured at the PVDD pin of the chip does not exceed 55V. Is it considered to exceed the normal specification value of 53.5V (the extreme specification value is 69V).

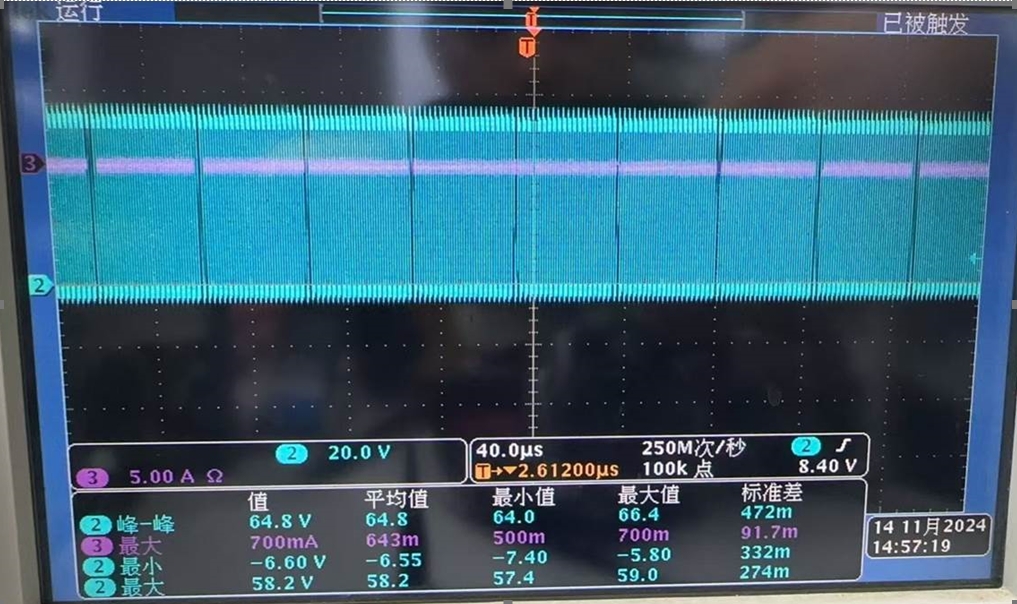

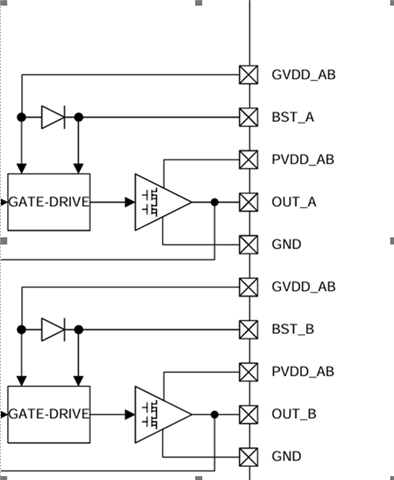

Also, using an oscilloscope to test that the low level between GVDD_AB and BST_A (the same for the other groups) is -6~-7V, is this normal and how can it be explained?

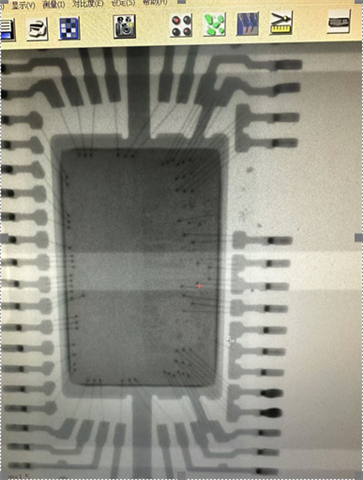

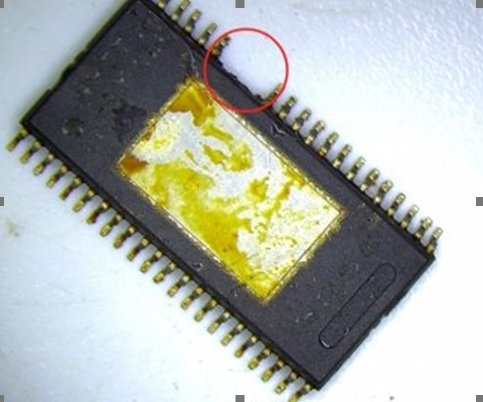

The damaged chip and X-ray photos are as follows (the yellow substance on the chip is rosin left behind when disassembling the chip)

Use an oscilloscope to test the waveform of -6~-7V at low level between GVDD_AB and BSTAA (the same for other groups):