Tool/software:

Hi team,

BCLK_POL is the second bit of Register0x07. When this IC is used as a Slave, is it correct to shift the timing of the Data to BCLK by setting this register, not to change the polarity of the BCLK input/output to fsync?

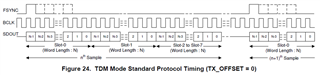

In addition, Figure 24/27 in the Datasheet has inverted polarity. Is this correct understanding correct as a diagram of the clock when this IC is used as a Master?

Regards,

Youhei MIYAOKA