Tool/software:

Dear Team,

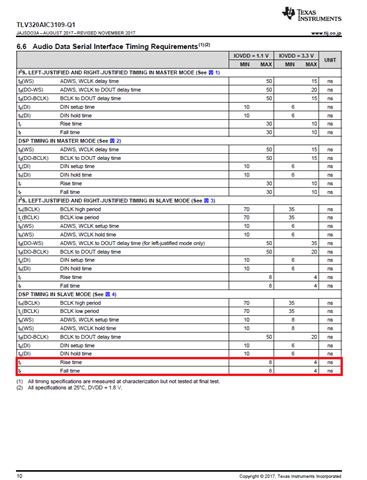

My customer is evaluating the 6PAIC3109TRHBRQ1 (TLV320AIC3109-Q1) on their system. They want to confirm the rise/fall time requirements described in “6.6 Audio Data Serial Interface Timing Requirements” in the data sheet.

For the applicable range of rise/fail time;

Q1: Unlike other items, BCLK or others are not specified, but are you aware that BCLK, WS, DI, DO are the target if this rise/fall time?

About rise/fail time 4ns;

Q2: On their system board currently under evaluation, the rise time and fall time are measured at 10% and 90% of the waveform, respectively, and the time is about 4.7 ns. On the data sheet, it is specified as 4ns (max), so please provide information such as "is it out of range?" or the measurement method is different (is it other regulation not 0%-90%?).

Best Regards,

Koshi Ninomiya