Tool/software:

Hello everyone,

i'm wondering if the TLV320AIC3268 is able for this setup :

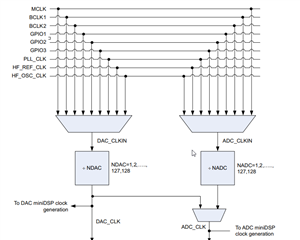

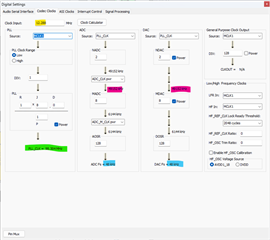

DAC Fs = ADC Fs = 48Khz, (MCLK = 12.288Mhz ; PLL_CLK = 98.304 Mhz ; ADC_CLK = DAC_CLK = 49152Khz)

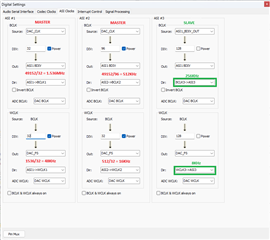

- ASI1 = I2S 16 bits - Master with WCLK = 48Khz

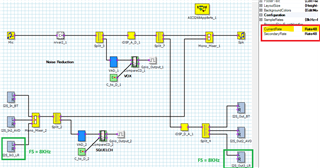

- ASI2 = I2S 16 bits - Master with WCLK = 16Khz (down sampling thanks to the WCLK and BCLK divider)

- ASI3 = I2S 16 bits - Slave with WCLK = 8Khz (how can it be done? as the WCLK divider seems to be available only if ASI is master)

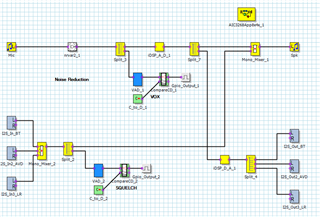

the sample rate of the miniDSP is 48Khz and is in charge to mix the 3 x ASI.

Do i need a ASRC for such configuration ?

Thank you for your help

Sebastien