Tool/software:

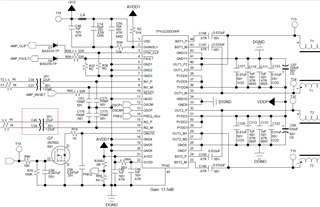

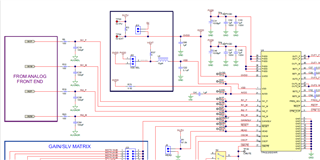

We design TPA3220 work on BTL mode(SCH as below) , but each day first time power up , TPA3220 go into PBTL mode, retry power up again , TPA3220 go into BTL mode .

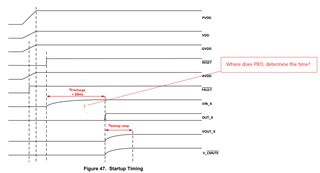

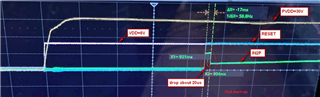

If the machine is turned off for more than 1 hour, restarting will enter PBTL mode.

We try to change C39/40 from 22uf to 1uF , the error entering PBTL mode remove. I am not sure this solution work or not , or only can use for some IC, we also can't find out the detail information about how to enter PBTL mode and determine the time point, relationship with power supply, reset pin, and other information. Please share more detail about how to go into PBTL mode and how to 100% not go into PBTL mode.