Tool/software:

Hi team,

I have three questions below

[Question 1]

If either OUTP or OUTN is shorted to PGND, at which stage does the output become Hi-Z?

A. DC Detect (Section 7.3.5)

B. Short-Circuit Protection and Automatic Recovery Feature (Section 7.3.6)

[Question 2]

If the output becomes Hi-Z due to process A., it is mentioned that a PVCC cycle is required for recovery.

Does this mean that PVCC must be lowered below a certain voltage and then restored to the supply voltage?

If so, what voltage should PVCC be lowered to, and for how long should it be maintained at that level?

[Question 3]

If the output becomes Hi-Z due to process B, it is mentioned that automatic recovery can occur by directly connecting FAULT and SD.

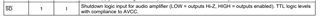

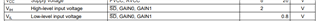

In this case, does the device recover when SD goes Low, or when it goes High?

Section 7.3.6 (Short-Circuit Protection and Automatic Recovery Feature) suggests recovery occurs at Low, while Section 5 (Pin Configuration and Functions) indicates that output is enabled at High. Which is correct?

Best regards,

Goto