Tool/software:

Hi all,

I am facing a noise/crackling problem with in my design using the PCM 1863 as ADC which is connected as clock master to a DSP (which sends the MCLK) on the digital side, which on its serial output is connected to a class D amplifier.

On the ADC I am using both a balanced and unbalanced input (not at the same time). On the analog frontend I implemented a voltage divider to archieve an approx 6.5dB voltage reduction to allow for higher input levels.

Only my low frequency woofer channel I can hear some soft crackling and pops (aside of the usual static noise) which I believe is noise picked up by the analog front end path since the noises stop if I am using the digital audio input to the DSP.

If I push the low end level around 40-50Hz using EQs in the DSP the noise gets louder. Also connecting a source (audio interface) to the design significantly raises the crackling noise level.

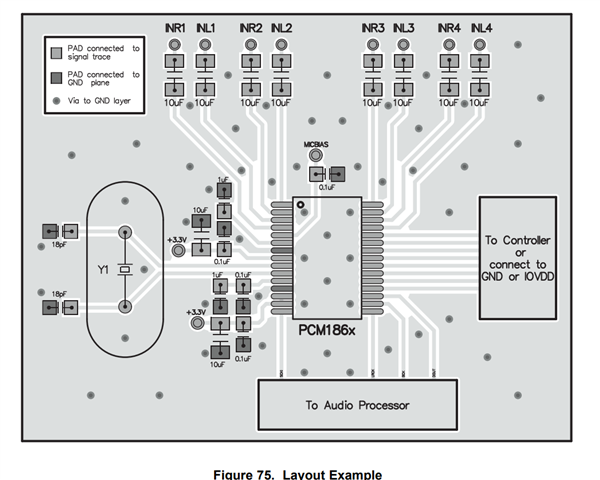

For the voltage divider I am using thin film resistors which should in theory result in a input impedance of approx. 14kOhm together with the ADCs input impedance. I am using a 4 layer board and the second layer is a GND plane below all the paths shown in the pictures.

The ADC is running at 96kHz 32bit setting and I am using some PGA (+3dB) and mixer gain scaling (-8.5dB for balanced) internally.

Can someone give me advice on possibilities how my layout and schematic can be improved regarding EMI and noise coupling?

Any other advices for potential design problems that could be causing the crackling noises?

Help would be much appreciated!

All the best,

Max