Tool/software:

Dear Expert,

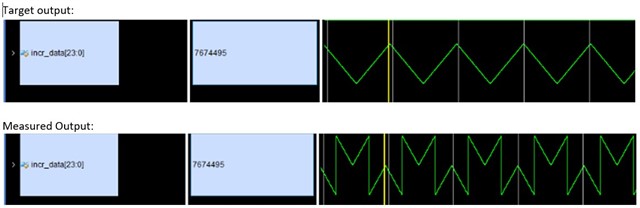

A customer is sending triangulated data from FPGA to PCM1780. It's 24bit data per channel with the sequence 24'h7F_FFFF~24'h00_0000,24'hFF_FFFF~24'h80_0000~24'hFF_FFFF,24'h00_0000~24'h7F_FFFF.... that is 24bit complement data cycling from largest to smallest an repeat...

Customer is expecting a triangular wave form, but found the measured output is not. It seems like the PCM1780 treated negative complement as positive number. (see picture description in below diagram).

Could you help to adv where may have gone wrong in the test?

Best Rgds,

Stanley