Tool/software:

目前我们想使用 STM32来控制 adc5140进行音频捕获,但是我们的 ADC 似乎无法正常工作,这是我们为这个 ADC 配置的寄存器。

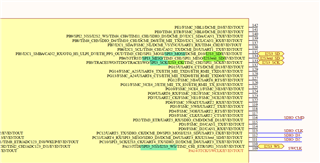

ADC_DATE_INPUT(0x00,0x00);/*选择寄存器的页码*/

ADC_DATE_INPUT(0x02 , 0x81);/*上电*/

ADC_DATE_INPUT(0x05 , 0x05);

ADC_DATE_INPUT(0x07 , 0x40);/*ASI_CFG0 registery音频输出配置*/

ADC_DATE_INPUT(0x08 , 0x20);/*ASI_CFG1 registery音频输出配置*/

ADC_DATE_INPUT(0x09 , 0x00);/*ASI_CFG2 registery音频输出配置*/

ADC_DATE_INPUT(0x0B , 0x00);/*ASI_CH1 registery音频输出配置*/

ADC_DATE_INPUT(0x13 , 0x02);/*设备配置为 从模式,并且时钟信号(BCLK 和 FSYNC)由外部 MCU 生成*/

adc_write_reg(0x14, 0x48);/* 配置采样率,48KHZ */

ADC_DATE_INPUT(0x16 , 0x08);/*MCLK(GPIO 或 GPIx)用作音频根时钟源(MCLK 与 FSYNC 的比率根据 MCLK_RATIO_SEL 设置而定)*/

ADC_DATE_INPUT(0x21 , 0x00);/*禁用输入端GPIO功能*/

ADC_DATE_INPUT(0x22 , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x23 , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x24 , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x25 , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x2B , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x2C , 0x00);/*禁用输入端GPI/O功能*/

ADC_DATE_INPUT(0x3B , 0x00);/*VREF设置为2.75 V,麦克风偏置为3.3*/

adc_write_reg(0x3C,0x20);

adc_write_reg(0x3D,0x60);

adc_write_reg(0x3E,0xC9);

adc_write_reg(0x3F,0x80);

adc_write_reg(0x40,0x00);

adc_CHx_CFGx(CH2_CFG0,0x20);

adc_CHx_CFGx(CH2_CFG1,0x60);

adc_CHx_CFGx(CH2_CFG2,0xC9);

adc_CHx_CFGx(CH2_CFG3,0x80);

adc_CHx_CFGx(CH2_CFG4,0x00);

adc_CHx_CFGx(CH3_CFG0,0x20);

adc_CHx_CFGx(CH3_CFG1,0x60);

adc_CHx_CFGx(CH3_CFG2,0xC9);

adc_CHx_CFGx(CH3_CFG3,0x80);

adc_CHx_CFGx(CH3_CFG4,0x00);

adc_CHx_CFGx(CH4_CFG0,0x20);

adc_CHx_CFGx(CH4_CFG1,0x60);

adc_CHx_CFGx(CH4_CFG2,0xC9);

adc_CHx_CFGx(CH4_CFG3,0x80);

adc_CHx_CFGx(CH4_CFG4,0x00);

adc_write_reg(0x6B,0x00);

adc_write_reg(0x73, 0xF0);IN_CH_EN寄存器

adc_write_reg(0x74, 0xF0);ASI_OUT_CH_EN 寄存器

adc_write_reg(0x75, 0xF4);PWR_CFG 注册

同时我们读取以下三个 registers 的状态:

寄存器地址:ASI_STS , 寄存器状态:ff

注册地址:DEV_STS0 , 注册状态:0

寄存器地址:DEV_STS1 , 寄存器状态:c0

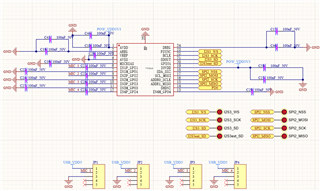

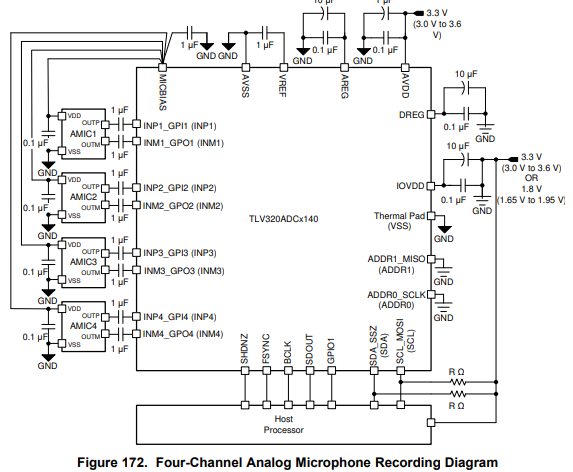

这是我们针对此 ADC 的电路设计原理图