Tool/software:

Hello everybody,

I have a problem with the PCM3120-Q1, where I measue data with the I2S interface.

I apply a sine wave with 5 kHz on the input of the ADC.

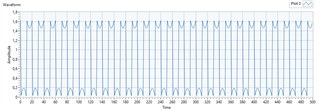

When I configure the I2S interface with 96 kHz (real frequency is 100 kHz) and 32 bit word length, the measured signal looks like this:

For me it looks like either there is a data conversion error or the signal is overshooting.

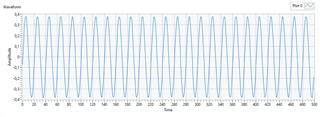

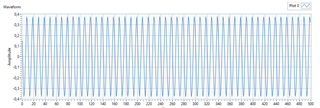

Anyway, when I configure the I2S interface at 100 kHz / 16 bit or 48 (real 50) kHz / 32 bit, the data looks correct.

So I assume, it's neither a data conversion error nor overshooting of the signal.

100 kHz / 16 bit

50 kHz / 32bit

My initialization of the PCM3120-Q1 looks like this:

// Set page to page 0x00 pcm3120_wr_reg(REG_PAGE_CFG, 0x00); // Disable sleep pcm3120_wr_reg(REG_SLEEP_CFG, 0x01); // Sleep according to datasheet: // "Wait for at least 1 ms to allow the device to complete the internal wake-up sequence" HAL_Delay(5); // Set ADC_FSCALE to 2d = "VREF is set to 1.375 V to support 1 VRMS for the differential input or 0.5 VRMS for the single-ended input" pcm3120_wr_reg(REG_BIAS_CFG, 0x02); // Set Channel 1 input type to "Line input" pcm3120_wr_reg(REG_CH1_CFG0, 0x80); // Set Channel 1 input impedance to "Typical 10 kOhm input impedance" pcm3120_wr_reg(REG_CH1_CFG0, 0x84); // Set Channel 1 gain to 20 dB pcm3120_wr_reg(REG_CH1_CFG1, 0x50); // Enable input Channel 1 pcm3120_wr_reg(REG_IN_CH_EN, 0x80); // Set ASI to I2S mode with 16 / 24 / 32 bit word length pcm3120_wr_reg(REG_ASI_CFG0, 0x70); // 32 bit word length // pcm3120_wr_reg(REG_ASI_CFG0, 0x60); // 24 bit word length // pcm3120_wr_reg(REG_ASI_CFG0, 0x40); // 16 bit word length // Enable ASI Channel 1 output pcm3120_wr_reg(REG_ASI_OUT_CH_EN, 0x80); // Power PLL and ADC channel pcm3120_wr_reg(REG_PWR_CFG, 0x60);

I'm using a STM32 µC as host controller. My I2S configuration there looks like this:

The only thing in the datasheet, where I found something related to this is the ASI_WLEN configuration, where it recommends to use 16bit word length with 10 kOhm input impedance (chapter 8.6.2.5 ASI_CFG0 -> ASI_WLEN):

ASI word or slot length. 0d = 16 bits (Recommended this setting to be used with 10-kΩ or 20-kΩ input impedance configuration) 1d = 20 bits 2d = 24 bits 3d = 32 bits

Can you help me fix this issue, or explain why 96 kHz / 32bit word length is not possible with this setup?

Thanks and best regards

Julian