Tool/software:

Hi,TI ' s experts

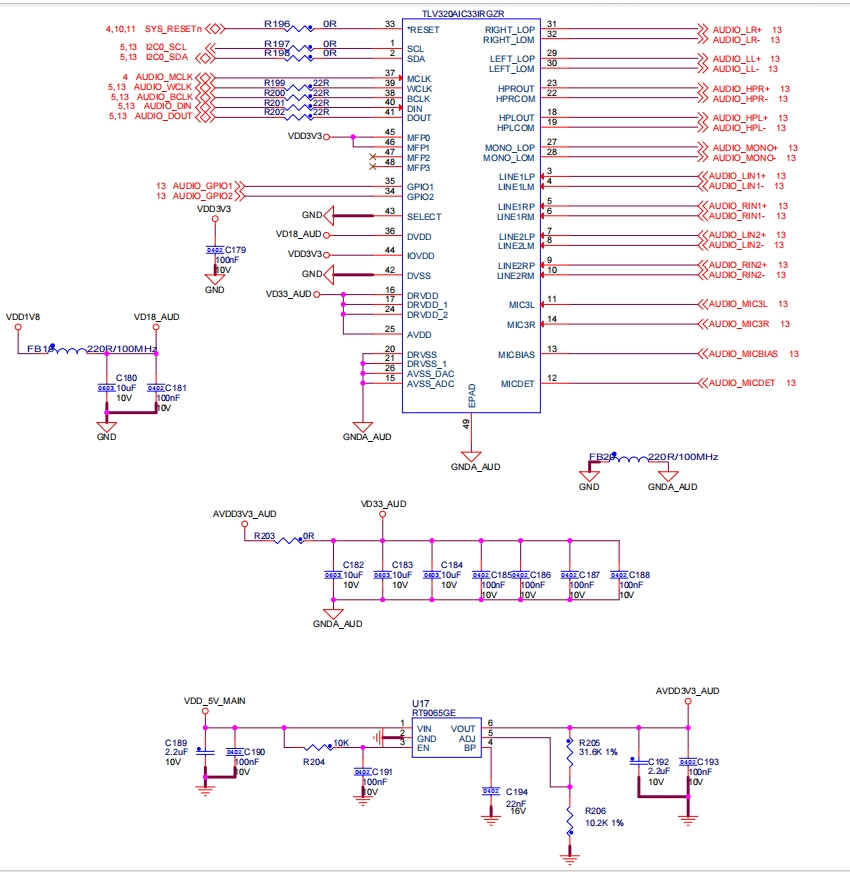

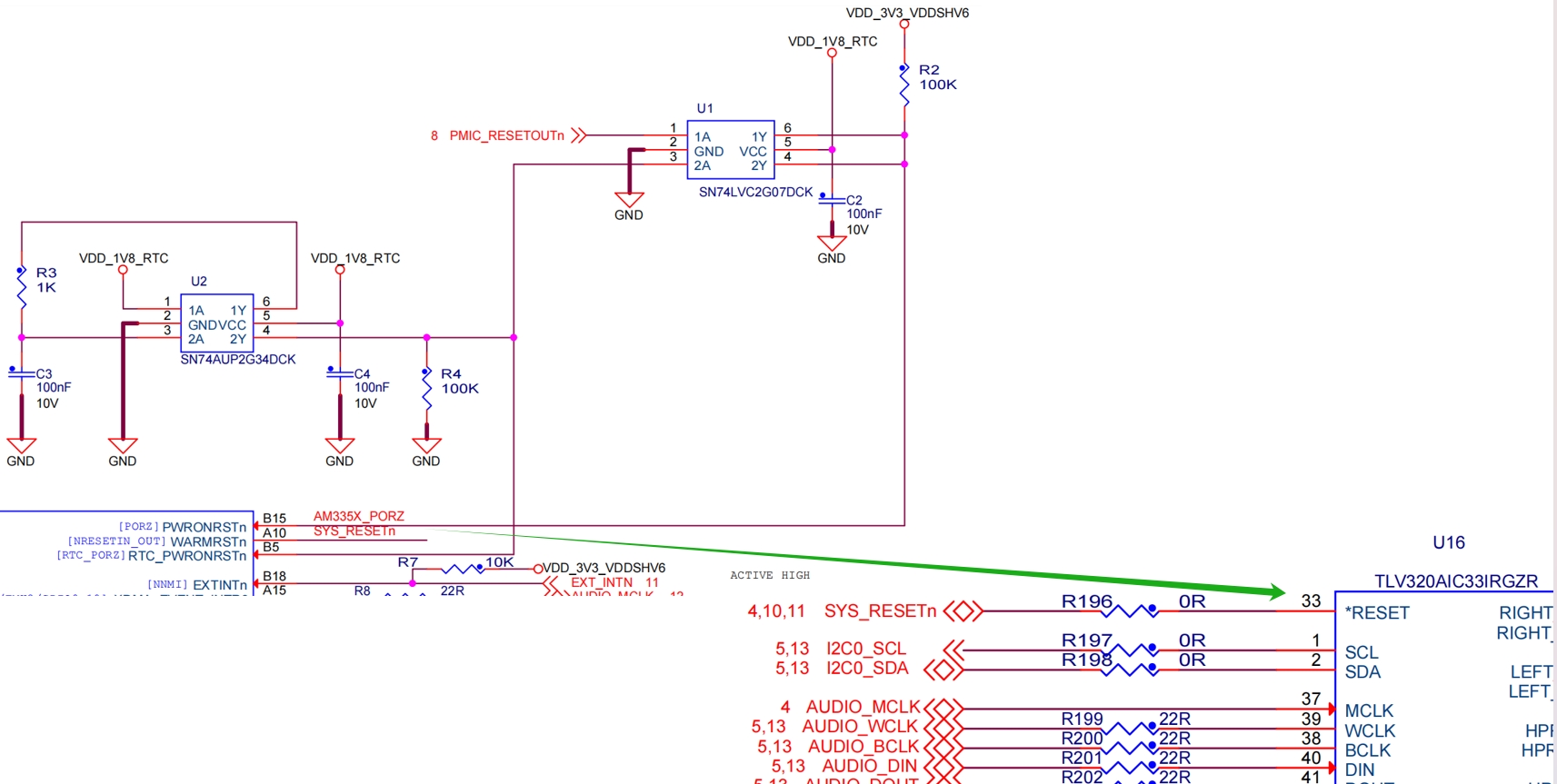

Our audio products have been using the TLV320AIC33/TLV330AIC3106 audio codec chips on the AM335x platform for many years. Recently, during customer use, a small number of devices have occasionally encountered issues where the sound card fails to play audio. The only way to restore normal operation on-site is by unplugging and replugging the external power supply. After such a procedure restores normal function, the issue may recur after a few days.

We've attempted the following steps:

1. When playback fails, we configure the Software Reset register of AIC3x via the i2cset command to perform a soft reset, then restart the audio application process (which internally initializes and configures AIC3x) to play an audio file. However, it was found that audio still couldn't be played.

2. Additionally, we used the i2cdump command to dump the current register settings and compared them before and after the issue occurred, finding no differences. Without powering off the motherboard, manually sending a reset signal to the RESET pin of the chip and performing a hard reset allowed normal playback of sound.

What could be causing this phenomenon, and what suggestions do you have for troubleshooting ???

(Internally, we tend to think that there is an abnormal working state within the audio chip; however, there is no definite conclusion yet on what causes this abnormal state - whether it is related to hardware or software.)

Regards,

LI MIN