Other Parts Discussed in Thread: TAS6424

Tool/software:

Hello,

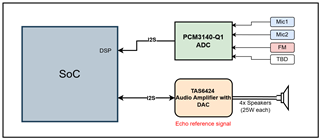

We are planning to use the PCM3140Q1 audio codec along with the TAS6424 audio amplifier in our system. Additionally, we aim to implement Adaptive Echo Cancellation (AEC) and need expert guidance on the following aspects:

-

Pin Mapping & Interface with SoC:

- Our SoC provides only WS (Word Select), SCK (Bit Clock), and SData (Data Line). How should we map the connections between the PCM3140Q1, TAS6424, and the SoC for optimal performance, considering AEC implementation?

- Are there any specific considerations or additional connections needed for proper synchronization and data flow?

-

MCLK Requirement:

- Since our SoC does not generate MCLK, we would like to confirm whether the PCM3140Q1 or TAS6424 can internally generate the Master Clock or if an external MCLK source is necessary.

- If an external MCLK is required, what are the recommended clock specifications?

We would greatly appreciate your expert input on the above points to ensure a robust design.

Looking forward to your valuable insights.

Regards,

Abhishek