Tool/software:

Hello, I want to implement TLV320AIC3204 to my new PCB project. I was inspecting the related documents about the IC and I seem to have a found a few contradictions.

1.The datasheet of TLV320AIC3204 (Page 8 Section 7.3 Recommended Operating Conditions) specifies that minimum LDOIN/HPVDD supply is 1.9V. But the document "SLAA557 (TLV320AIC3204 Application Reference Guide)" Page 1 Register 10 Bit 0 says the following,

0: When Page-1, Reg-10, D1=1, then LDOIN input range is 1.5V to 1.95V

1: When Page-1, Reg-10, D1=1, then LDOIN input range is 1.8V to 3.6V

(This is at page 125 of the document)

and the default value of this register is 0 there this implies that during start-up LDOIN should powered up with a maximum voltage 1.95V and LDOIN supply's minimum supply voltage is actually 1.5V.

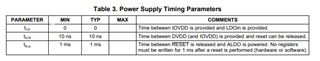

and also the document "SLAA492A (TLV320AIC32x4 Power Supply Sequencing)" says the following (at Page 2 Section 2 External DVDD and AVDD Power Supply Sequence)

The recommended power sequence for this configuration is to provide all supplies simultaneously. A

typical configuration in such a case is to use a single 1.8-V supply for IOVDD, DVDD, LDOin, and AVDD

So this again implies that LDOIN can be powered with voltage lower than 1.9V.

My question is, I am planning to supply the LDOIN and IOVDD from the same 3.3V LDO at start-up, would this cause any issues? What is the real voltage for LDOIN supply?

Also I noticed that by default AVDD is tied to DVDD with a 10Kohm resistor this allows AVDD to ramp up when DVDD is provided. The Figure-1 at the document "SLAA492A" shows that DVDD is connected to LDOIN/HPVDD so if I enable the DVDD by pulling the LDO_SELECT pin of the TLV320AIC3204 DVDD get immediately turned on when I apply the LDOIN supply ?

If it does, does the DVDD get's set to it's default set voltage (which is controlled by Page 1 Register 2 Bits 6-7 = 00 is the default value which corresponds to 1.72V).