Tool/software:

Dear Texas Instruments Technical Support Team,

I'm writing regarding performance issues we've observed with the TLV320AIC3204 audio codec during our recent qualification testing for a new product design.

Our testing has revealed three specific concerns that we'd appreciate your insights on:

-

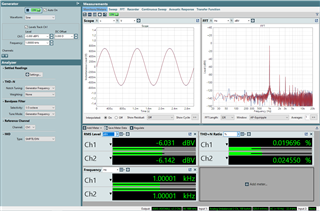

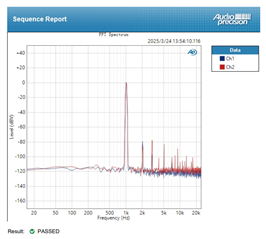

ADC Noise Floor Performance: We're measuring higher than expected noise floor values in the ADC path. Our measurements show approximately -87 dBFS noise levels , which is significantly higher than what we expected based on the datasheet specifications.

-

DAC Output Gain Variation: We've observed unusually high output gain in the DAC path. The measured output levels exceed our expected values based on our configuration settings.

-

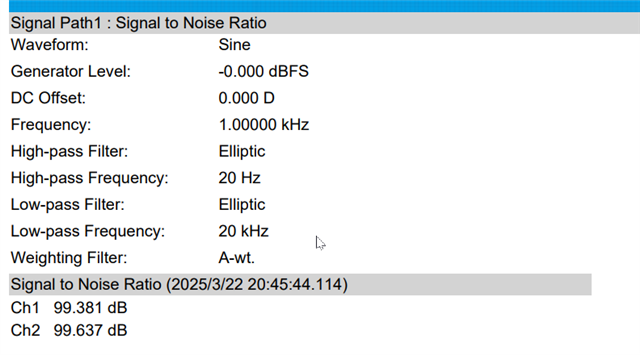

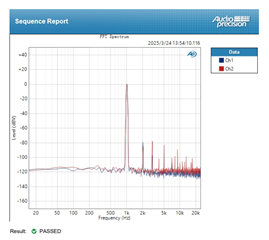

Channel-to-Channel THD+N Discrepancy: Perhaps most concerning is the significant difference in THD+N performance between left and right channels. Our measurements show:

- Left Channel (Ch1): 0.048664% THD+N

- Right Channel (Ch2): 0.021597% THD+N

This represents more than a 2:1 ratio difference between channels, which exceeds our product specifications for channel matching.

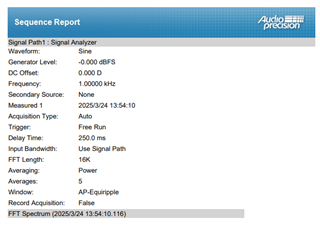

We've attached comprehensive test reports performed using ABTEC audio analysis equipment. All measurements were taken under controlled conditions with the following setup:

- 48kHz sample rate

- 24-bit resolution

- Standard test signals at 1kHz

- Input/output via professional audio interfaces with verified performance

Could you please advise if these observations are within normal operating parameters for the TLV320AIC3204? If not, we'd appreciate your recommendations for addressing these issues, whether through register configuration adjustments or potential hardware modifications to our implementation.

We're currently in the final stages of product development, so your prompt assistance would be greatly appreciated.

Thank you for your support.

Best regards,

Allen Su

Please check the

Please check the