Tool/software:

TLV320ADC6140 is configured to receive PGA gain change settings from a host over I2C based on user settings with a Microphone preamp. This is required when a very low output mic requires slightly more gain that the external pre-amp can't provide.

A differential pre-amp filter with 22uF capacitive coupling drives either IN1+/- or IN2+/- with up to two XLR inputs to the system.

Other settings: DRE/AGC disabled, I2S-slave/24-bit with single data output pin, input impedance = 2.5k, Vref quick charge = 3.5ms, In-cap quick charge = 2.5ms, Vref=2.75V

The routine for changing PGA gain is as follows: reset the ADC via PWR_CFG.ADC_PDZ = 0, change the appropriate PGA register CHx_CFG1 (limited to 0d42), then re-enable the ADC via PWR_CFG.ADC_PDZ = 1.

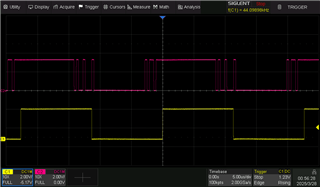

It takes some time of rapidly changing the gain at ~10ms up and down, but eventually the signal to the host is lost on one or both inputs (its random). Signal loss means the serializer no longer sends the expected PCM data (eg. can no longer step the signal level at the input into overdrive and observe the sign-bit moving up).

I can confirm that I2S and I2C is still functioning as expected (PGA values read back correctly), and signal is still present at IN1+/- or IN2+/- with a DC bias offset (~1.5V).

Is there a delay required with ADC_PDZ = 1 when setting PGA gain? Do i need to monitor CHx status as part of the PGA gain change process? Am I doing something else wrong?