Tool/software:

Hello,

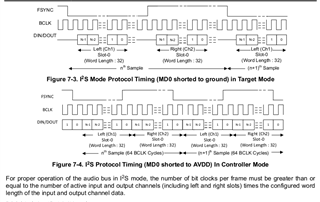

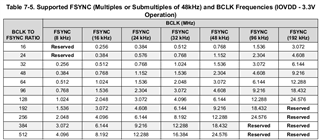

I am looking to operate the TAC5242 in Target mode using an I2S interface with 32b word length and a sample rate of 192k. To satisfy the requirements of the I2S interface that means I must use > 64 BCLK to FSYNC ratio since the first BCLK is not used. This means I must generate a BCLK of 18.432MHz per table 7-5 (shown below). What are the consequences of not being able to make the 18.432 clock perfectly? If I am off by 100ppm is that an issue? Is it ok if the BCLK to FSYNC ratio is still 96 even though the absolute FSYNC and BCLK frequencies are off?

Thank you for your help in advanced.