Other Parts Discussed in Thread: TAS2505

Tool/software:

In our hardware design for the automotive sector, we are using the TAS2505 Audio IC. During operation and in the short/open circuit mechanisms, there is no issue.

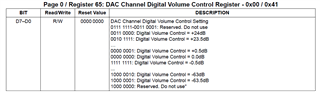

However, after the microcontroller completes the TAS2505 initialization, I hear a crackling sound from the speaker. Additionally, every time I perform an open circuit check, since TAS2505 is being turned off and on again, I hear the same sound. Could this be related to the gain settings? I need to perform continuous polling once per second, and I hear this sound every time. I don't want to set the gain to 0 dB and then back to 6 dB every time. Reinitializing through I2C could take time and cause delays, as the sounds need to be handled in real time.