Part Number: TAS2563

Tool/software:

Hello,

I'm working with TAS2563 on a device that has DC input (not battery). We are using external boost configuration (since we have +12v rail). I'd like to know possible ways to limit the power consumption of the amp. Here are my questions:

- Is there a way to check if the amp is configured properly to use external boost? I currently have the 'boost enable' unchecked and boost mode = always off.

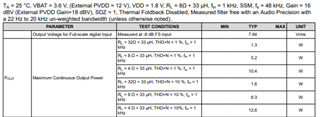

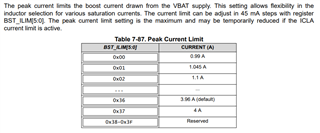

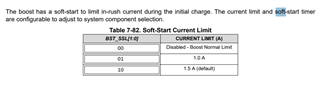

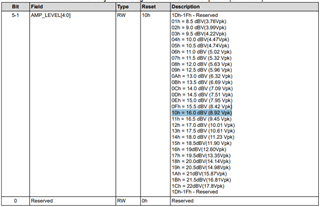

- The 'peak current limit' under 'channel gain'. Is this acting on the output (to speaker) or input? and does it still work on external boost (mode = always off)? If it's limiter on output, would that mean that the voltage will be the same as PVDD (in this case +12v)?

- Can we somehow use the VBAT battery tracker and Brown-Out Protection on non-battery powered device (to limit peak consumption of amp when total consumption of the device is high)?

- Any other tips to manage power consumption?

- Is there a way to import EQ values from external file (e.g csv)?

Thanks in advance!