Tool/software:

Hi,

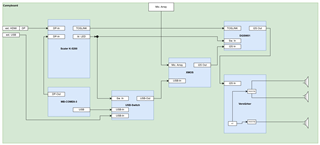

in our system we use an audio amplifier in 2.1 configuration with two TAS5756M. The I2S input comes from a switch board which selects between a SPDIF (TOSLINK from a scaler board) and a I2S signal. If the audio level has a minimum level and we switch back and forth between the two signal sources suddenly the subwoofer amplifiers overdriven. After I do a power cycle of the audio amplifier the volume is back to normal.

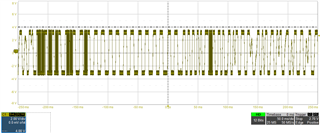

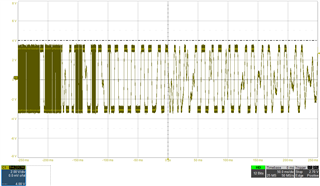

I try to analyze the I2S input data in the amplifier and can measure that during the switch time the I2S signal will change the frequency.

Do you have a hint where the problem is?

Thank you for your help.

BR

martin