Other Parts Discussed in Thread: PCM1863

Tool/software:

Hello E2E Experts,

Good day.

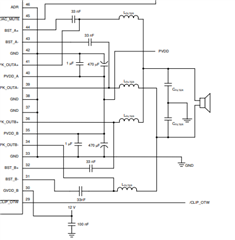

My Project contains 1x PCM1863 as audio source and 2x TAS3251 to realize 2.1 audio system. The PCM1863 Audio Input and one TAS3251 in BTL 2.0 Mode is working fine. The TAS3251 device in PBTL mode for subwoofers has no pwm output signals. The I2S signal is complete and correct and the clock is configured correctly. No errors are reported by FAULT pin, Clip OTW pin and fault register 0x5E and 0x5F (both = 0x0). The mode pin has 3V3 level and the SPK_INB+ and - are connected to GND via 0R resistor. The device in PBTL mode uses same parts as device in BTL mode and is in Post-Filter configuration.

Are there more configurations to do before TAS3251 has an output signal in PBTL mode? Are there additional registers for diagnostics? How can I check if DSP configuration was successful?

Regards,

TICSC