Tool/software:

Dear,

Customers using PCM1690 often experience; After changing the following configuration, the probability decreases and only exists at the moment of startup, duration of about 30 seconds;

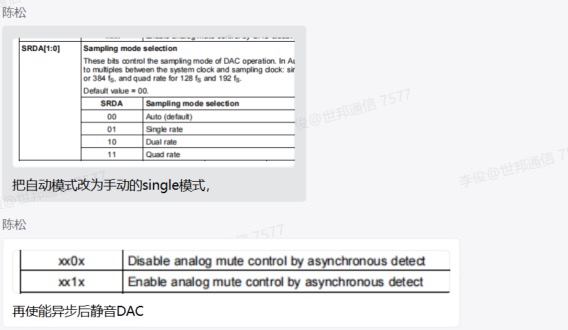

Change the automatic mode to manual single mode and mute the DAC after enabling asynchronous mode,