Tool/software:

Hi!

I hand-wired the codec board from the TLV320 eval kit to my Nordic Semiconductor processor devkit to test out the codec and so far I've been completely unable to make it make sound except for a pop in the headphones when it initializes. I'm feeding 3.3V from a power supply into the 3.3V net and into HPVDD/LDOIN and I'm pretty sure I have the switches and everything set correctly to use the internal LDO for DVDD and AVDD. If I measure some spots on the board with my multimeter: LDO_SEL is ~3.3V, IOVDD is ~3.3V, DVDD is 1.708V, AVDD is 1.704V. I'm successfully communicating with it via I2C most of the time, though I do get write or readback failures on some powerups.

I'm attempting to configure it to run at 48kHz from my 6.144MHz MCLK signal with no PLL and then use the beep generator to make some sound even if only the I2C commands and clock input is OK, but again nothing so far.

I've tried moving my configuration commands around so they happen before or after MCLK is active, right now I have it all happening after MCLK has been toggling for awhile.

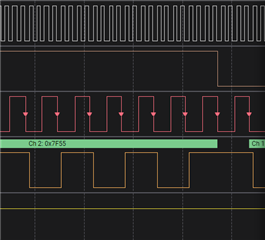

The relevant setup code is in a code block below, and I've attached a Saleae capture showing what all of the signals are doing (I2C, MCLK, BCLK, LRCLK (WCLK), DIN, RESET).

Please help! I'm trying to get this working ASAP to verify our hardware design.

Thanks,

Glen

k_sleep(K_MSEC(1000));

retcode |= tlv320_write(0, 0x01, 0x01); // Software reset

k_sleep(K_MSEC(100));

// === CLOCK SETUP for MCLK = 6.144 MHz ===

// We will use MCLK directly, so PLL is not needed

while (tlv320_write(0, 0x04, 0x00)); // CODEC_CLKIN = MCLK

// NDAC = 1, MDAC = 2 for 6.144 MHz -> 48 kHz with DOSR = 128

while (tlv320_write(0, 0x0B, 0x01)); // NDAC = 1

while (tlv320_write(0, 0x0C, 0x01)); // MDAC = 1

while (tlv320_write(0, 0x0D, 0x00)); // DOSR MSB = 0

while (tlv320_write(0, 0x0E, 0x80)); // DOSR LSB = 128

// Interface settings

while (tlv320_write(0, 0x1B, 0x00)); // I2S, 16-bit word length

// while (tlv320_write(0, 0x1D, 0x01); // low bits: 00: BDIV_CLKIN = DAC_CLK, 01: BDIV_CLKIN = DAC_MOD_CLK

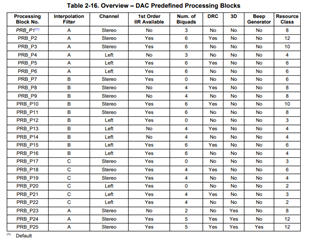

while (tlv320_write(0, 0x3C, 0x08)); // DAC processing block = PRB_P8

// Enable Master Analog Power:

while (tlv320_write(1, 0x01, 0x08)); // Disable crude AVDD

// Enable internal LDO:

while (tlv320_write(1, 0x02, 0x01)); // Enable AVDD LDO with analog blocks powerered up

while (tlv320_write(1, 0x7B, 0x01)); // REF charging time = 40ms

while (tlv320_write(1, 0x14, 0x25)); // HP soft stepping config

while (tlv320_write(1, 0x0A, 0x00)); // Common mode settings

// Route DAC outputs

while (tlv320_write(1, 0x0C, 0x08)); // Route Left DAC to HPL

while (tlv320_write(1, 0x0D, 0x08)); // Route Right DAC to HPR

// Class AB amplifier setup

while (tlv320_write(1, 0x03, 0x00)); // PTM mode for DAC

while (tlv320_write(1, 0x04, 0x00));

// Set output volume

while (tlv320_write(1, 0x10, 0x14)); // HPL gain = 10dB

while (tlv320_write(1, 0x11, 0x14)); // HPR gain = 10dB

while (tlv320_write(1, 0x09, 0x30)); // Power up HPL and HPR drivers

k_sleep(K_MSEC(2500)); // TLV320 app guide says to wait 2.5 seconds for soft stepping to take effect to avoid pops

// Page 0 DAC power-up

while (tlv320_write(0, 0x3F, 0xD6)); // Power up both DACs, route L/R channels

while (tlv320_write(0, 0x40, 0x00)); // Unmute DAC

// Test beep

LOG_ERR("TLV320 BEEP START");

retcode |= tlv320_quick_write(0, 0x49, 0x5F); // MSB

retcode |= tlv320_quick_write(0, 0x4A, 0x00); // MID

retcode |= tlv320_quick_write(0, 0x4B, 0x00); // LSB

retcode |= tlv320_quick_write(0, 0x48, 0x00);

retcode |= tlv320_quick_write(0, 0x47, 0x80);

}