Tool/software:

I have a TLV320ADC5140 hooked up to an STM32H750 dev board.

I've configured the serial audio peripheral on the STM32 for 16-bit audio, 4 output slots and 16kHz sample rate.

The TLV320ADC5140 is configured for 4 single-ended input channels, outputting 4 slots in 16-bit TDM mode - the device operates as a slave.

Unfortunately, the TLV320ADC5140 is not detecting the sample rate nor the BCLK to FSYNC ratios on the ASI bus, only reporting errors for both.

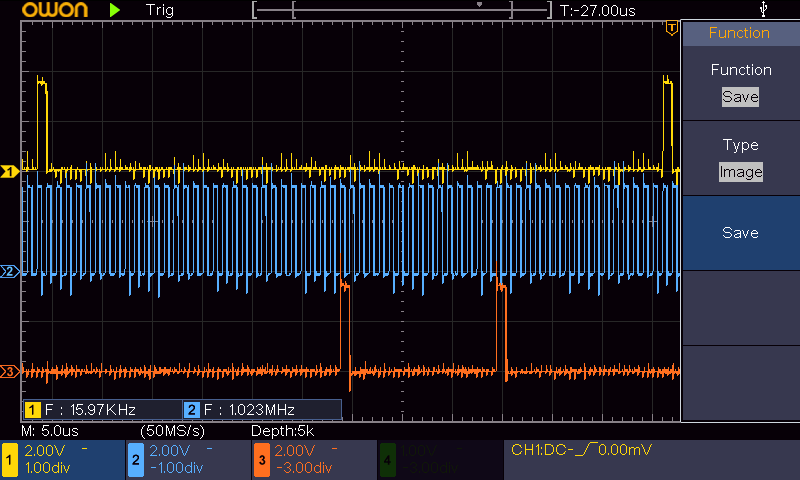

Here's a scope trace of the serial bus:

The yellow trace is FSYNC, blue is BCLK and the orange is DATA. As you can see from the frequency measurements, the FSYNC is at 16kHz, BCLK is 1.024MHz and there are 64 BCLK cycles between FSYNC pulses.

Here is a dump of the TLV320ADC5140 registers after initialisation of the serial audio bus:

10:38:19.575 -> [0x02] SLEEP_CFG = *0x81 [0x00]

10:38:19.575 -> [0x05] SHDN_CFG = 0x05 [0x05]

10:38:19.575 -> [0x07] ASI_CFG0 = *0x00 [0x30]

10:38:19.575 -> [0x08] ASI_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x09] ASI_CFG2 = 0x00 [0x00]

10:38:19.575 -> [0x0B] ASI_CH1 = 0x00 [0x00]

10:38:19.575 -> [0x0C] ASI_CH2 = 0x01 [0x01]

10:38:19.575 -> [0x0D] ASI_CH3 = 0x02 [0x02]

10:38:19.575 -> [0x0E] ASI_CH4 = 0x03 [0x03]

10:38:19.575 -> [0x0F] ASI_CH5 = 0x04 [0x04]

10:38:19.575 -> [0x10] ASI_CH6 = 0x05 [0x05]

10:38:19.575 -> [0x11] ASI_CH7 = 0x06 [0x06]

10:38:19.575 -> [0x12] ASI_CH8 = 0x07 [0x07]

10:38:19.575 -> [0x13] MST_CFG0 = 0x02 [0x02]

10:38:19.575 -> [0x14] MST_CFG1 = 0x48 [0x48]

10:38:19.575 -> [0x15] ASI_STS = 0xFF [0xFF]

10:38:19.575 -> [0x16] CLK_SRC = 0x10 [0x10]

10:38:19.575 -> [0x1F] PDMCLK_CFG = 0x40 [0x40]

10:38:19.575 -> [0x20] PDMIN_CFG = 0x00 [0x00]

10:38:19.575 -> [0x21] GPIO_CFG0 = 0x22 [0x22]

10:38:19.575 -> [0x22] GPO_CFG0 = 0x00 [0x00]

10:38:19.575 -> [0x23] GPO_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x24] GPO_CFG2 = 0x00 [0x00]

10:38:19.575 -> [0x25] GPO_CFG3 = 0x00 [0x00]

10:38:19.575 -> [0x29] GPO_VAL = 0x00 [0x00]

10:38:19.575 -> [0x2A] GPIO_MON = 0x00 [0x00]

10:38:19.575 -> [0x2B] GPI_CFG0 = 0x00 [0x00]

10:38:19.575 -> [0x2C] GPI_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x2F] GPI_MON = 0x00 [0x00]

10:38:19.575 -> [0x32] INT_CFG = 0x00 [0x00]

10:38:19.575 -> [0x33] INT_MASK0 = 0xFF [0xFF]

10:38:19.575 -> [0x36] INT_LTCH0 = *0x40 [0x00]

10:38:19.575 -> [0x3B] BIAS_CFG = 0x00 [0x00]

10:38:19.575 -> [0x3C] CH1_CFG0 = *0x20 [0x00]

10:38:19.575 -> [0x3D] CH1_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x3E] CH1_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x3F] CH1_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x40] CH1_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x41] CH2_CFG0 = *0x20 [0x00]

10:38:19.575 -> [0x42] CH2_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x43] CH2_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x44] CH2_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x45] CH2_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x46] CH3_CFG0 = *0x20 [0x00]

10:38:19.575 -> [0x47] CH3_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x48] CH3_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x49] CH3_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x4A] CH3_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x4B] CH4_CFG0 = *0x20 [0x00]

10:38:19.575 -> [0x4C] CH4_CFG1 = 0x00 [0x00]

10:38:19.575 -> [0x4D] CH4_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x4E] CH4_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x4F] CH4_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x52] CH5_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x53] CH5_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x54] CH5_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x57] CH6_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x58] CH6_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x59] CH6_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x5C] CH7_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x5D] CH7_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x5E] CH7_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x61] CH8_CFG2 = 0xC9 [0xC9]

10:38:19.575 -> [0x62] CH8_CFG3 = 0x80 [0x80]

10:38:19.575 -> [0x63] CH8_CFG4 = 0x00 [0x00]

10:38:19.575 -> [0x6B] DSP_CFG0 = 0x01 [0x01]

10:38:19.575 -> [0x6C] DSP_CFG1 = 0x40 [0x40]

10:38:19.575 -> [0x6D] DRE_CFG0 = 0x7B [0x7B]

10:38:19.575 -> [0x70] AGC_CFG0 = 0xE7 [0xE7]

10:38:19.575 -> [0x73] IN_CH_EN = 0xF0 [0xF0]

10:38:19.575 -> [0x74] ASI_OUT_CH_EN = *0xF0 [0x00]

10:38:19.575 -> [0x75] PWR_CFG = *0xE0 [0x00]

10:38:19.575 -> [0x76] DEV_STS0 = *0xF0 [0x00]

10:38:19.575 -> [0x77] DEV_STS1 = *0xE0 [0x80]

10:38:19.575 -> [0x7E] I2C_CKSUM = *0x18 [0x00]

The DEV_STS registers are showing that the channels are enabled and powered up. As you can see, ASI_STS is reporting 0xFF but I'm unsure as to why.

Any pointers would be greatly appreciated..