Tool/software:

There are two codecs tlv320aic34 connected to mcasp1 on am62x, both A and B part of the codecs are being used, which means we have four codecs share the same cpu dai, they also share the same AXR0 for send and AXR1 for transmission. Pin LINE2LP LINE2LM LINE2RP LINE2RM are for line inputs and LEFT_LOP LEFT_LOM RIGHT_LOP RIGHT_LOM are for line outputs. I need to playback/record on the 4 codecs simultaneously.

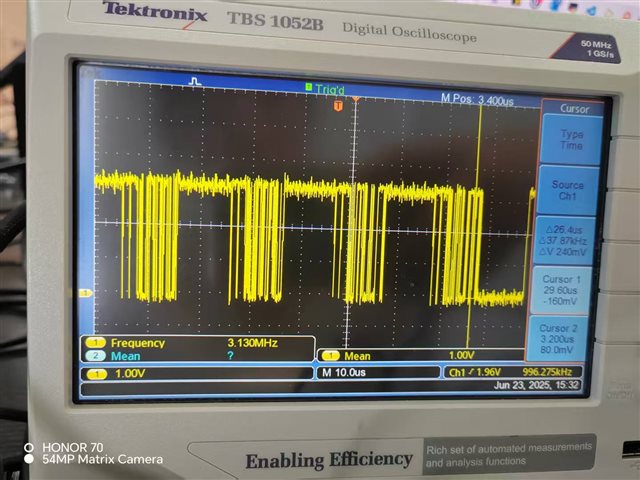

My question is do I have to create a new machine driver for this hardware configuration or simple-audio-card driver could apply? For me, I create a new machine driver with one cpu dai and four codecs, cpu is doing master, it has 8 slots and each 24 bit. data format is dsp_b. But I cannot hear any sound when playback. It seems working well from programming side with BCLK, FCLK and MCASPI outputting correct waveform. I set the LEFT and RIGHT DAX MUX to DAC_L3/R3 by amixer so that DAC is directly connected to LINEOUT. when I play the mute wav, the output on line out is a sine wave with relatively stable frequency of 1.18MHZ and amplitude. when I play other normal wav source, the output is a sine wave with continuously varying frequency and amplitude. The frequency is so high for human to hear. Please help how to figure out the problem.

The device tree is below:

&{/} {

sound {

compatible = "simple-audio-card-xxx";

simple-audio-card,name = "xxx";

#address-cells = <1>;

#size-cells = <0>;

simple-audio-card,widgets =

"Line", "codec1 Line In",

"Line", "codec1 Line Out",

"Line", "codec2 Line In",

"Line", "codec2 Line Out",

"Line", "codec3 Line In",

"Line", "codec3 Line Out",

"Line", "codec4 Line In",

"Line", "codec4 Line Out";

simple-audio-card,routing =

"codec1 LINE2L", "codec1 Line In",

"codec1 LINE2R", "codec1 Line In",

"codec1 Line Out", "codec1 LLOUT",

"codec1 Line Out", "codec1 RLOUT",

"codec2 LINE2L", "codec2 Line In",

"codec2 LINE2R", "codec2 Line In",

"codec2 Line Out", "codec2 LLOUT",

"codec2 Line Out", "codec2 RLOUT",

"codec3 LINE2L", "codec3 Line In",

"codec3 LINE2R", "codec3 Line In",

"codec3 Line Out", "codec3 LLOUT",

"codec3 Line Out", "codec3 RLOUT",

"codec4 LINE2L", "codec4 Line In",

"codec4 LINE2R", "codec4 Line In",

"codec4 Line Out", "codec4 LLOUT",

"codec4 Line Out", "codec4 RLOUT";

simple-audio-card,dai-link@0 {

reg = <0>;

format = "dsp_b";

bitclock-master = <&cpu>;

frame-master = <&cpu>;

bitclock-inversion;

cpu: cpu {

mclk-fs = <384>;

sound-dai = <&mcasp1>;

clocks = <&audio_refclk0>;

system-clock-direction-out;

dai-tdm-slot-num = <8>;

dai-tdm-slot-width = <24>;

dai-tdm-slot-tx-mask = <1 1 1 1 1 1 1 1>;

dai-tdm-slot-rx-mask = <1 1 1 1 1 1 1 1>;

};

codec_ports{

codec: codec@0 {

sound-dai = <&audio_codec1>;

dai-tdm-slot-num = <8>;

dai-tdm-slot-width = <24>;

dai-tdm-slot-tx-mask = <1 1 0 0 0 0 0 0>;

dai-tdm-slot-rx-mask = <1 1 0 0 0 0 0 0>;

};

codec1: codec@1 {

dai-tdm-slot-num = <8>;

dai-tdm-slot-width = <24>;

dai-tdm-slot-tx-mask = <0 0 1 1 0 0 0 0>;

dai-tdm-slot-rx-mask = <0 0 1 1 0 0 0 0>;

sound-dai = <&audio_codec2>;

};

codec2: codec@2 {

dai-tdm-slot-num = <8>;

dai-tdm-slot-width = <24>;

dai-tdm-slot-tx-mask = <0 0 0 0 1 1 0 0>;

dai-tdm-slot-rx-mask = <0 0 0 0 1 1 0 0>;

sound-dai = <&audio_codec3>;

};

codec3: codec@3 {

dai-tdm-slot-num = <8>;

dai-tdm-slot-width = <24>;

dai-tdm-slot-tx-mask = <0 0 0 0 0 0 1 1>;

dai-tdm-slot-rx-mask = <0 0 0 0 0 0 1 1>;

sound-dai = <&audio_codec4>;

};

};

};

};

};

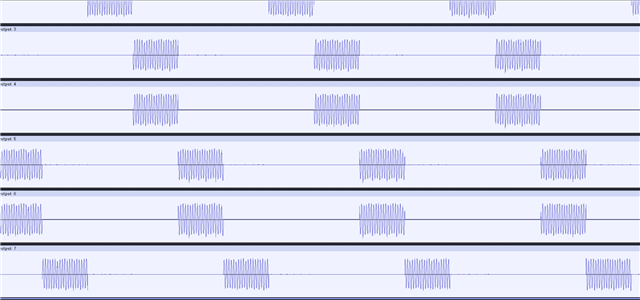

FCLK

FCLK  MCLK

MCLK  BCLK I find it is a little different from the exact value I set. I use the audio reference clock for mclk and the parent is <&k3_clks 157 7>; Maybe I should use one of the codec as master. But I think it is not the reason that the output is noise.

BCLK I find it is a little different from the exact value I set. I use the audio reference clock for mclk and the parent is <&k3_clks 157 7>; Maybe I should use one of the codec as master. But I think it is not the reason that the output is noise.