Other Parts Discussed in Thread: TLV320AIC3254

Tool/software:

Hi experts,

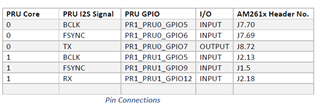

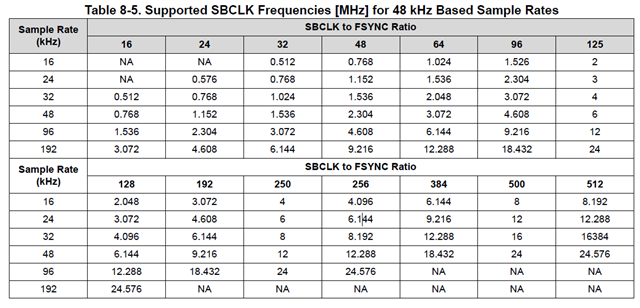

Currently we are planning to use the I2S interface that is emulated using the PRUs on I2S.

However, it seems like we cannot provide the I2S signals Fsync & BCLK for TAS2781,

Is there any Audio Converter that can provide these signals to create a point to point connection with AM261 PRUs so that we can the audio amplifier connected to AM261x directly ?

Regards,

Alex