Tool/software:

質問させてください。

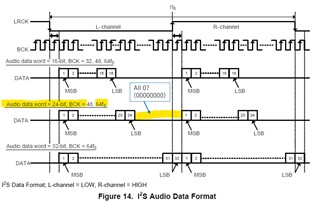

PCM5102Aにてサンプリングレート256kHzを実現しようとしています。FPGAよりLRCK, BCK, and SCK を入力する構成で考えています。各クロックの周波数はLRCK:256kHzBCK:16.384MHz (fs×64)SCK:16.384MHzでも動作しますでしょうか。SCKに関しての関係性の制約がデータシートには記載されていないので問題ないと考えています。(PCM5102Aはスレーブ動作で通信フォーマットはI2Sです。)

%MCEペーストビン%