Tool/software:

Hi,

1. When operating at Fs=192 kHz with the following settings, the gain is +6dB. When operating at Fs=48 kHz or 96 kHz by changing the CCLK, the gain is also +6dB.

I could not find the specification of gain +6dB on the data sheet, but is this correct operation?

2. As shown in the attached measurement results, the output level differs between Single-end and Single-end w/high common mode. Is it the specification of this IC that the output changes depending on the pin setting regardless of the input level?

TAA5242 MDx setting and Input_Output level - コピー.xlsx

< Setting >

The following settings are made in the Controller mode of the ADC.

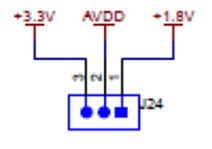

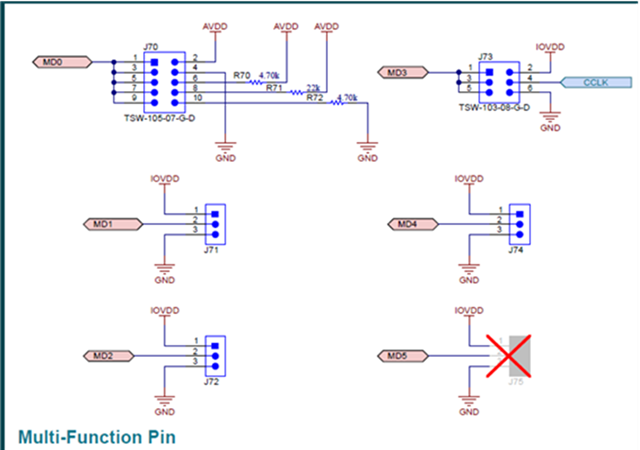

MD0: Short to AVDD (Controller I2S Mode)

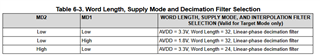

MD2:1: 2’b01 (CCLK/128)

MD3: 24.576MHz CCLK input

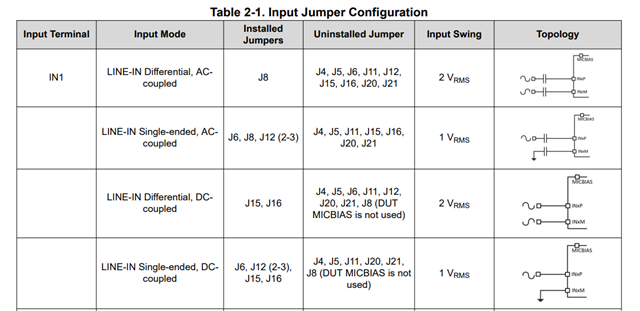

MD5:4: 2’b10 Single-Ended input on INxP; AC-Coupled only

*For measurement, the Digital Serial of the APx555 is connected to the pin header of the External ASI of the EVM.

Best Regards,

Nishie