Tool/software:

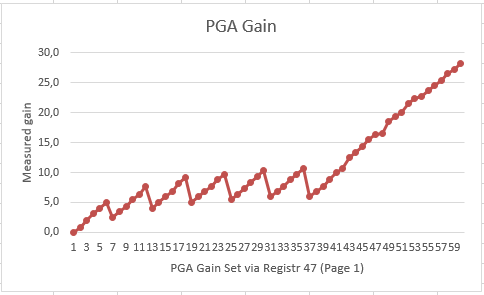

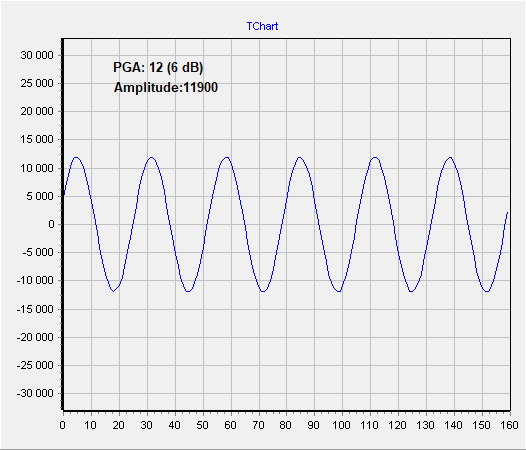

I have encountered an inconsistency in PGA Gain setting. When I gradually increase the value in Page 1 Register 47 the measured gain doesn't increase gradually, but there are drops in gain at some values. Please see included graph.

The drops in gain are at the following Page 1 Register 47 values: 12 (6 dB), 24 (12 dB), 36 (18 dB), 48 (24 dB), 60 (30 dB), 72 (36 dB)

I should note that AGC is switched off.