Other Parts Discussed in Thread: PCM9211, DIX4192

Tool/software:

Hi,

I'm exploring whether the DIX9211 would be a suitable transceiver for Ultranet

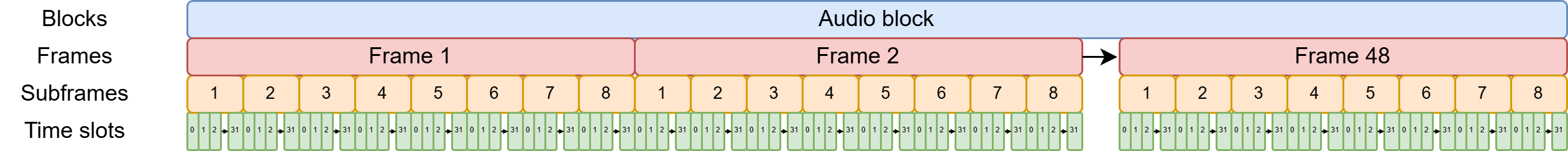

To summarize, one half of an Ultranet cable is a twisted pair carrying 8 channels of 48 kHz audio muxed together onto a 192 kHz AES3 signal.

The data looks something like this:

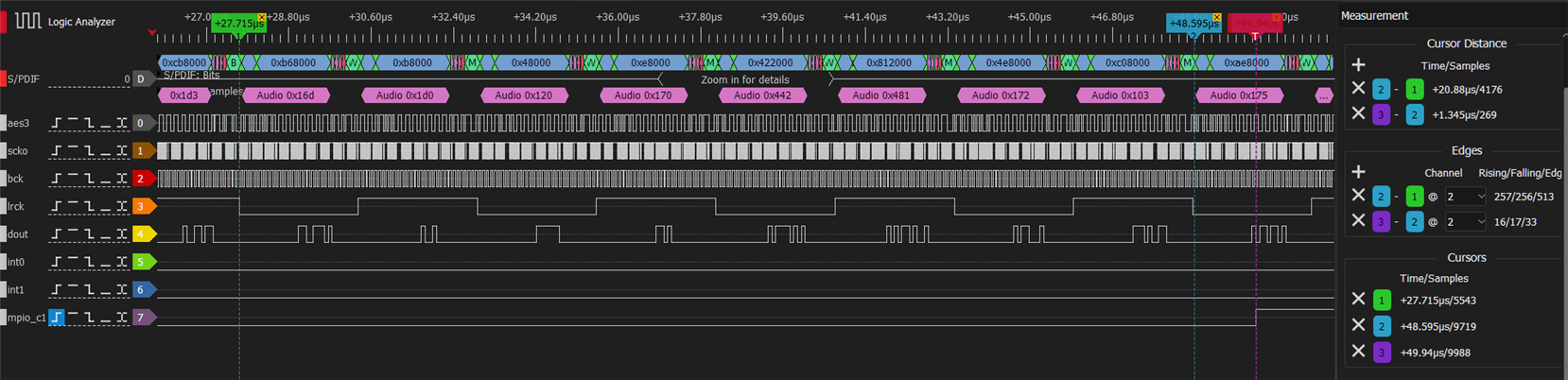

Sync/demuxing is done with the help of LRCK and the BFRAME.

Currently, I'm testing the DIR part of the chip; the output will go into an FPGA to do channel demuxing, but right now I'm just looking at my logic analyzer.

The chip seems to be working correctly; decoding works just fine.

However, I just noticed the horrendous delay between a B-frame preamble and the BFRAME signal actually being raised (which, after re-looking at the datasheet seems normal).

Here is a logic analyzer capture.

Is there an alternative way of signaling the B-frame that would be more presice?

Or if not possible with the chip is there another that wouldn't have such delay?

Thanks,