Other Parts Discussed in Thread: AM5728,

Tool/software:

Hi,

I have a custom board based on am5728 SOC running TI linux SDK 9.03 and I want to port driver for TLV320AIC3262 device.

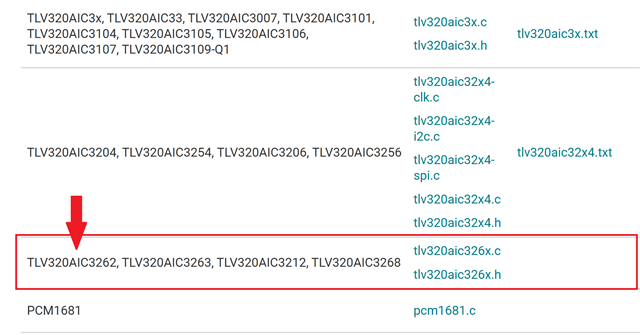

But I don't see any driver file for this device in sound/soc/codecs/ directory.

Please guide me with the steps needed.

-Vishal