Tool/software:

Hi team,

The audio signal input from the ADC is not being sent from the DSP to the DAC, yet a signal is being output.

Despite the MIC being OFF (no audio signal being sent from the DSP), the signal input to the ADC is being output.

The input format is the same as in Figure 7-15.

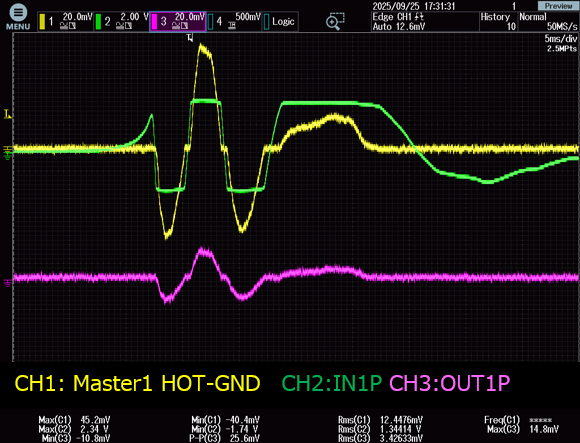

The waveform is attached below.

As shown in the diagram, when the ratings for IN1P and IN1M are exceeded, signals are generated only at OUT1P and OUT1M.

When an input exceeding the rating is applied, what operation is specified as the intended behavior?

Is there a possibility that signals could leak only from the DAC side CH?

The register settings are as follows.

w a0 00 00 # Set page 0

w a0 01 01 # Software Reset

w a0 02 09 # Wake up with AVDD > 2v and all VDDIO level

w a0 0a 00 #GPIO1 is disabled

w a0 0d 02 # GPI1 is GPI

w a0 0f 60 # CCLK is GPI1

w a0 10 50 # Configure DOUT as Primary ASI (PASI) DOUT

w a0 1a 60 # PASI I2S, 24 bit format

w a0 29 30 # PASI Ch2 on Right slot 0

w a0 32 50 # PASI Fs=48KHz with auto clock configuration

w a0 34 48 # PLL always enabled with fractional allowed and from fixed clk frequency

w a0 35 02 #MSB=10

w a0 37 f0 #24.576MHz MCLK, multiple of 48k (this is auto shifted to outputting 44.1k when MCLK is supplied as 22.5792MHz)

w a0 38 80 # Use internal BCLK for FSYNC generation in controller mode

w a0 39 40 # Set controller mode BCLK/FSYNC ratio to 64 = h40

w a0 76 8c #Input Channels 1 enabled; Output Channels 1, 2 enabled

w a0 78 c0 #ADC, DAC Powered Up

Best Regards,

Ryu.