Tool/software:

Hello,

My customer has some questions for AIC1110.

1)

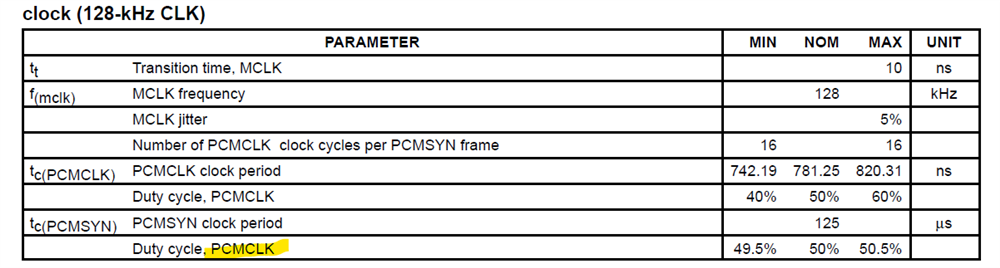

The below is from the datasheet.

Please see the yellow marked one. It says PCMCLK. But I think it is a typo and it should be PCMSYN.

Is this understanding correct?

2.

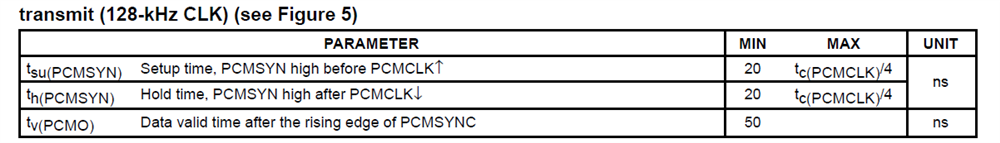

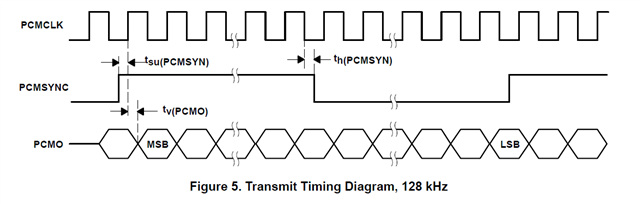

If it is correct, this PCMSYN have to be 50% duty. And the below is also from the datasheet.

Both hold/setup has MAX value. The customer's board seems lie violating this mmax value.

From the datasheet description, the rising edge of PCMCLK looks like latch point for PCMSYNC signal.

So the below is my understanding. Is it correct?

<Setup>

MIN: 20nsec -> If this min value is violated, PCMSYNC(Low to High) could not be latched at this cycle and could be latched at the next cycle.

MAX: PCMCLK/4 -> If this max value is violated, PCMSYNC(Low to high) could not be latched at this cycle and could be latched at the previous cycle.

<Hold>

MIN: 20nsec -> If this min value is violated, PCMSYNC(High to Low) could not be latched at this cycle and could be latched at previous cycle.

MAX: PCMCLK/4 -> If this max value is violated, PCMSYNC(High to Low) could not be latched at this cycle and could be latched at the next cycle.

3)

Then they would like to know waht could happen in the below 2 case.

Case 1: Violating tsu(PCMSYN)_MAX and th(PCMSYN)_MIN

Case 2: Just violating tsu(PCMSYN)_MAX

I think PCMI/O data bit shift (misalignment) could happen in both case. What do you think?

4)

When bit shift(misalignment) happens due to violating the above setup/hold violating, will it recover once the violation is removed?

Regards,

Oba