Hello,

I'm having quite a hard time trying to make it work. And there is not much documentation on using the board without a computer.

I supply power through the W5 test wire, 5v from the Stellaris board. Everything seems to be powered properly. I write the DAC registers using I2c, and this seems to work too (I read the registers with the control software, and their are changed accordingly to what I did).

I have a MCLK of 6MHz generated automaticaly (?!?). And it is 12Mhz when usb is plugged. Can I use this 6Mhz to clock the DAC? (I can also provide another clock on GPIO1 from the Stellaris).

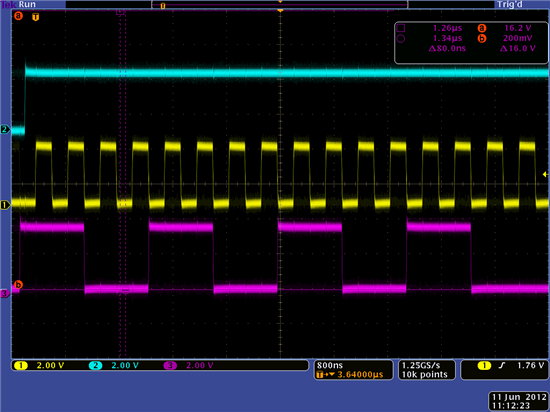

I send SPI data with the Stellaris, and check them on a scope, their are correct. But when I plug them on the DAC, they drop from 3.3 to about 1v. (BCLK, WCLK and DIN are configured as inputs)

Ideas? Comments? Examples?

Fabien