I am using the ADC data overflow event (via INT1) to trigger an "Audio Clip" LED on my custom board. I want the ADC to overflow when my Line1 input exceeds 0dBv (1.4v peak = 1VRMS), To accomplish this I have routed IN1_L/R to the PGA_L/R via a 40k resistor, and set CM1 to LPGA_P/M via a 40k resistor. I have also set the PGA gain to 0dB and the ADC gain to +6db (since the full scale input voltage required to produce a full scale ADC output is .5VRMS and I want to clip at 1.0VRMS, which is 6dbv higher than .5VRMS).

However, the ADC never overflows with the above settings. If I increase the ADC gain to +6.5db, the ADC will clip at 1.04VRMS. I suspect that the PGA is saturating before the ADC so that the ADC never overflows. Is this correct?

My main question is this:

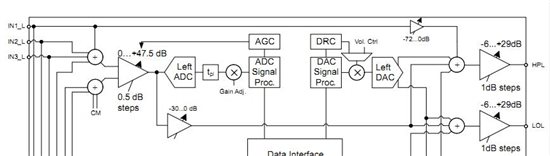

Is the gain device for the ADC ("ADC Channel Volume" Registers 0, 83 &84) physically located BEFORE or AFTER the ADC?? The reason I ask is, if it is AFTER the ADC (per Fig 1-1 of the datasheet - shown below), its setting should have no effect on the ADC overflow. However, my experiments indicate that it definitely DOES affect the overflow signal level.

Below is Fig. 1-1 from the datasheet. I assume the box labeled "Gain Adj." is the "ADC Channel Volume". Notice that it is AFTER the ADC, which means its setting should not affect the level at which the ADC overflows...

Also, what is the function of the boxes labeled tpl and tpr?

Any guidance on this issue would be much appreciated.