Hi,

I have two questions regarding the configuration of DIX4192.

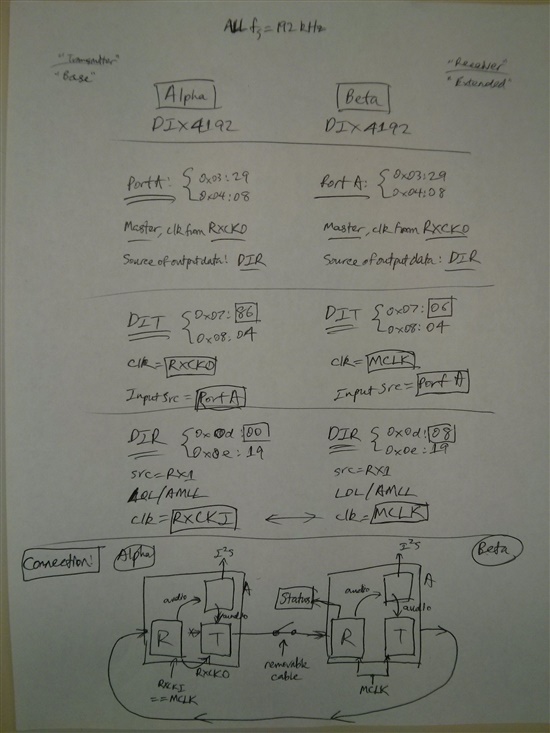

First questions is related to register 15 (Receiver Status Register 3) and 'OSLIP Error'. I use Port A to output DIR data in "Master Mode" with RXCLKO as clock source (Register 3: 0x29, and register 4: 0x08), I do not use Port B (but I set register 5: 0x41 to mute Port B, and register 6: 0x0). Now, if I enable OSLIP interrupt in register 17 (= 0x01) and read the status from it (register 0x15) I got an OSLIP error indicated all the time. My receiver part works, but I am a little bit confused as I understand the description in register 15 that this error occurs only if I use a slave configuration of the Port A or B for output DIR. Do I miss something?

Second one is regarding the 'Receiver Loss of Lock' (LOL) option in register 0x0E. In my application I have a receiver which will locked to transmitter (also DIX4192) and play audio (192kHz), it might happen that somebody removes the cable totally so that I will lose lock. If user plugs calbe in again it should work as before very quick. In most cases that works very well with activated "LOL" option (my configuration of register 0x0E in that case is: 0x19), but sometimes it will result in toggling nLock on receiver. I measured already RXCLKO which looks good, but that state of toggling nLock (which you can, of course, hear also in audio) will not go to an stable state even after a relly long time. If I do not use the "LOL" option it looks good for me, but it takes more time to activate audio again after loss of lock.

Best regards,

Max