Hello

Our customer wants to use two devices which have an audio serial I/O thru AIC3262.

Their signal flow is ASI2_in to ASI1_out mixing with ADC signal, ASI1_in to DAC and ASI2_out.

And they want to use AIC3262 as master device.

Now I'm trying it on PPS using two Serial Audio Interface #1 and Serial Audio Interface #2.

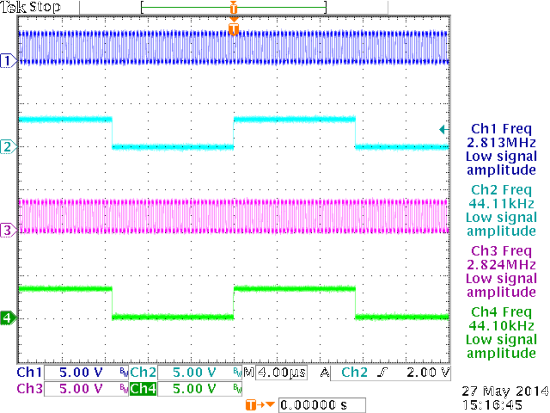

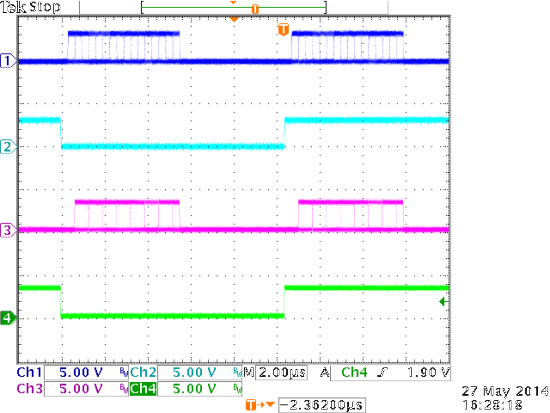

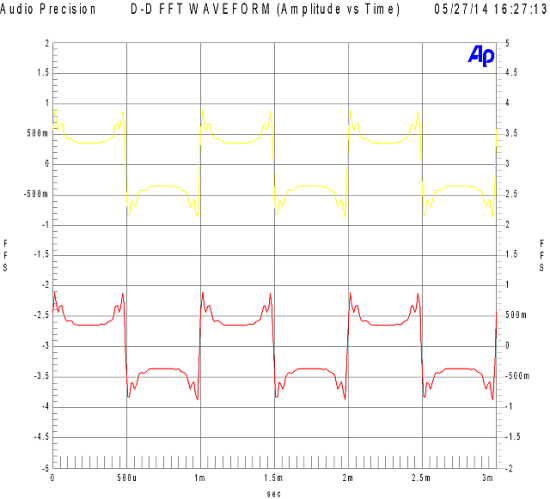

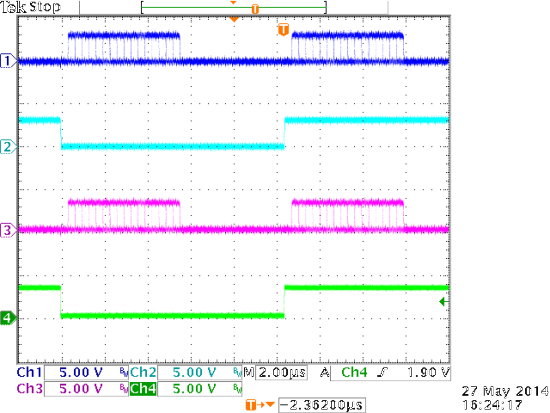

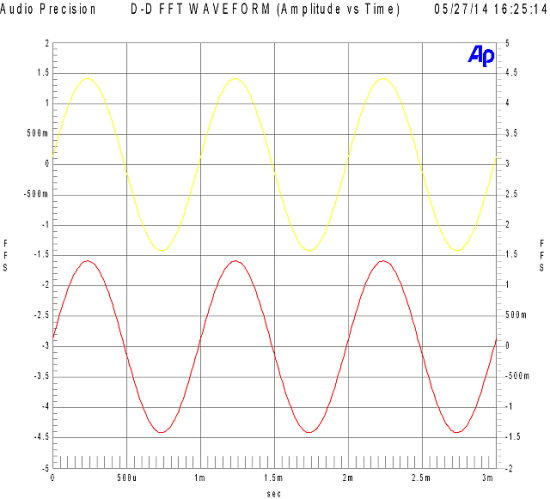

But I can't get clear output signal of SAI1_out and SAI2_out by AP with PSIA.

1st Question:

Is their signal flow possible, if AIC3262 is master and two audio signal interfaces are same sample rate?

2nd Question:

If the 1st Question is not possible, I want to propose that they use ASI1 as 4-channel interface.

But I2S_in and I2S_out component of PPS can be set as only 2-channel interface.

Please teach me the way to use ASI1 as 4-channel.

Best Regards,

Ito