Hello

I am using the TLV320AIC3254EVM-K Evaluation Board.

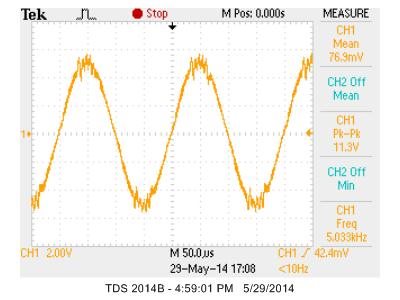

When I route the audio signal form IN1 through MAL/MAR to line outputs (without using DSP) from the AIC3254 CS software, providing a sine wave at the input produces a near perfect sine wave at the output.

Non-Distorted sine wave when analog input is routed to analog output by passing DSP processor

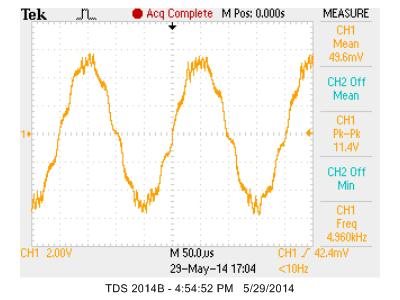

However when I route IN1 through DSP_A_DSP_D (using PurePath as shown in the above image) to line output, Providing a 5000Hz sine wave signal to the input produces a distorted waveform at the output.

And the distortion of the waveform (shape of the wave) changers when the parameters in the Digital settings -> Clocks/Interfaces panel of the AIC3254 CS software (PLL parameters R,J,D,P and NADC, MADC, etc) are changed.

Distorted sine wave when routed through DSP processor

My application requires the use of the DSP.

I tried to use R,J,D,P parameters generated by PLL Calculator in the AIC3254 but still can not get the required output (5000Hz sine waveform).

How ever low frequencies (bello 1000Hz) are produced correctly at the output.

Could you please let me know how to config the Clock interface parameters correctly.

Thank you in advance,