Dear e2e!

We are working with TLV320AIC3106 codec in our own board.

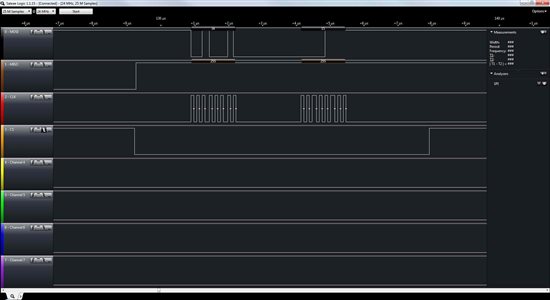

For controlling of the codec SPI interface is used (SCLK=5.4 MHz).

As the digital audio data serial interface the I2S interface is used (SCLK=250 kHz).

To the master clock input (MCLK) is applied a signal with 2.066 MHz.

We need to make numerous reconfiguration of codec during its work (under "reconfiguration" I mean changing PGA gain or connection/disconnection of analog inputs from PGA or analog outputs from DACs).

For example, we send periodically two blocks of commands to the codec:

< First block >

1) connect MIC3L to the left ADC (Reg17 = 0x0f);

2) disconnect DAC_L1 from LEFT_LOP/M (Reg82 = 0x7F);

3) disconnect DAC_R1 from LEFT_LOP/M (Reg85 = 0x7F);

< Second block >

1) disconnect MIC3L from the left ADC (Reg17 = 0xff);

2) connect DAC_L1 to LEFT_LOP/M (Reg82 = 0x80);

3) connect DAC_R1 to LEFT_LOP/M (Reg85 = 0x80);

Period between sending of each block of commands: few seconds and more.

Each reconfiguration command is sent to the codec via SPI interface. Format of the command: < number of a control register >, < data to be set >, < 10us pause >, < number of next control register > ... etc.

The problem is, that after sending of several of such blocks of commands (from 10 to 100) codec begins to transfer data from ADC directly to LEFT_LOP/M output (through DAC). So after we send first block of commands (connect MIC3L to the left ADC and disconnect DAC_L1/R1 from LEFT_LOP/M ) we HEAR A SIGNAL FROM MIC3L IN THE LEFT_LOP/M OUTPUTS !!!

It is seems, that the signal is transfered directly through ADC an DAC of codec ... through SW-D1 of codec (see "simplified block diagram" on datasheet SLAS509E).

But we can't control this switch directly...

We have tried:

1) to read back the control registers of the codec after the beginning of this parasite transfer. Registers 80...85 are equal to 0x00. LEFT_LOP/M seems to be disconnected, but, in the real world, signal from MIC3L is transfered to the LEFT_LOP/M;

2) to powerdown the DACs (Reg37=0x00). This transfer is dissapeared! But it isn't a solution, because we plan to use these DACs for translating of a external signal, that comes from a external CPU via I2S interface;

3) to disconnect DIN, DOUT and BCLK pins of codec from external CPU. Doesn't help. Parasite transfer is steel exist.

We would be very appreciate for any help and suggestions about this issue. For our purposes we need two independed ADC and DAC channels, which could be connected or disconnected to the input or output amplifiers of a codec.

May be there is some ERRATA on TLV320AIC3106, which describes some similar problems....

With many thanks in advance!

Vitalii