I am using the ADC PCM4202 and I have a problem with the THD+N:

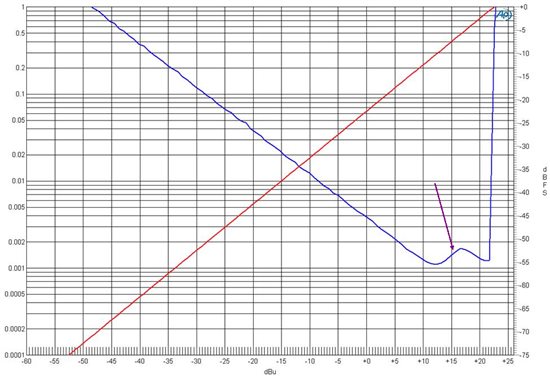

THD +N rise up at high level of input signal. See the next figure (Blue: THD+N; Red: Input level):

I can’t get the -105 dB of THD+N that specifies datasheet.

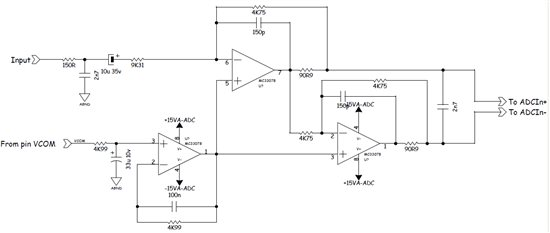

My board has every decoupling capacitors like demo board although my input analog circuit is different from the demo board. See next figure:

The ADC is setting in slave mode, HPFD disable, dual rate with clock auto-detection and fSCKI = 256 fs, fs= 96 Khz.

How could I improve the THD+N in this conditions? Thanks very much.