Dear Justin,

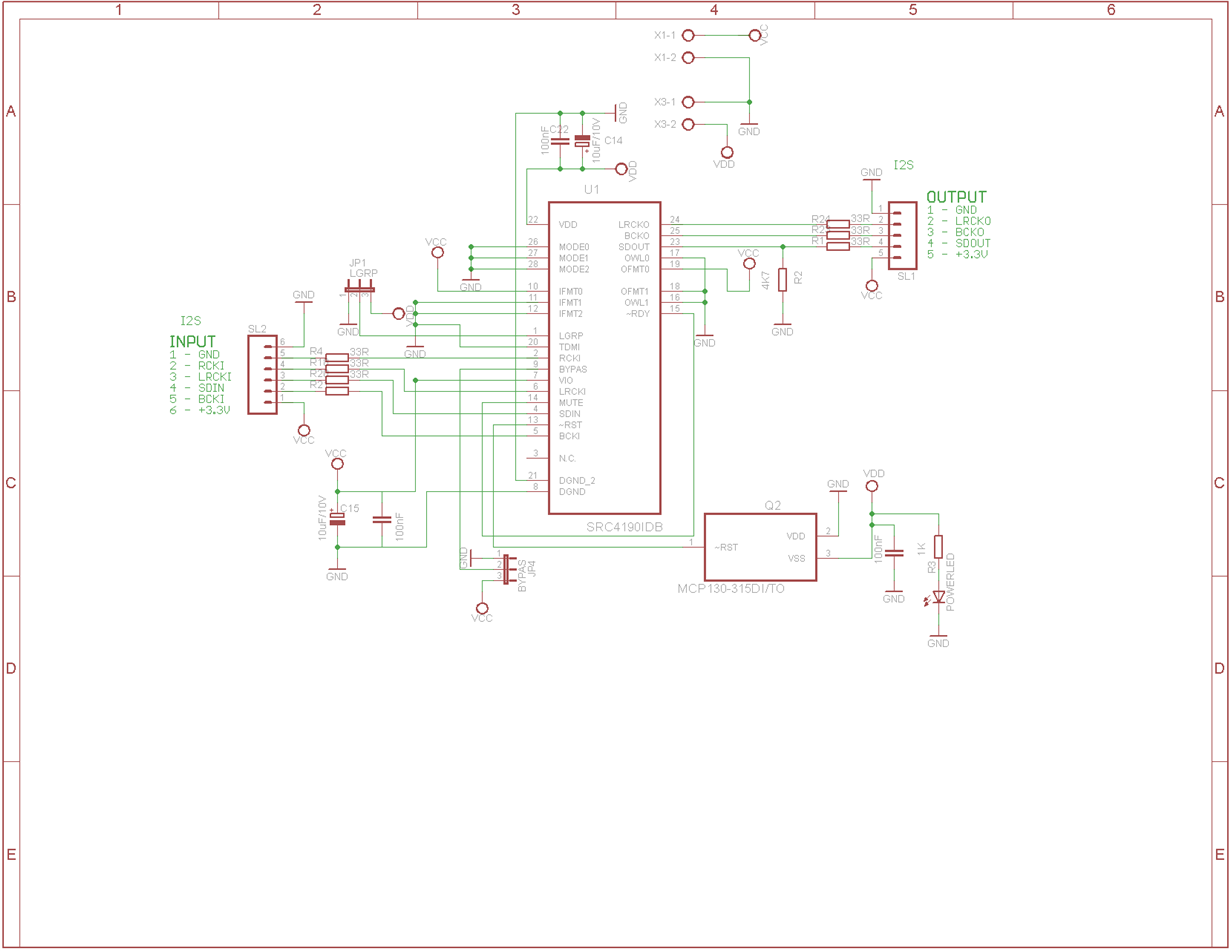

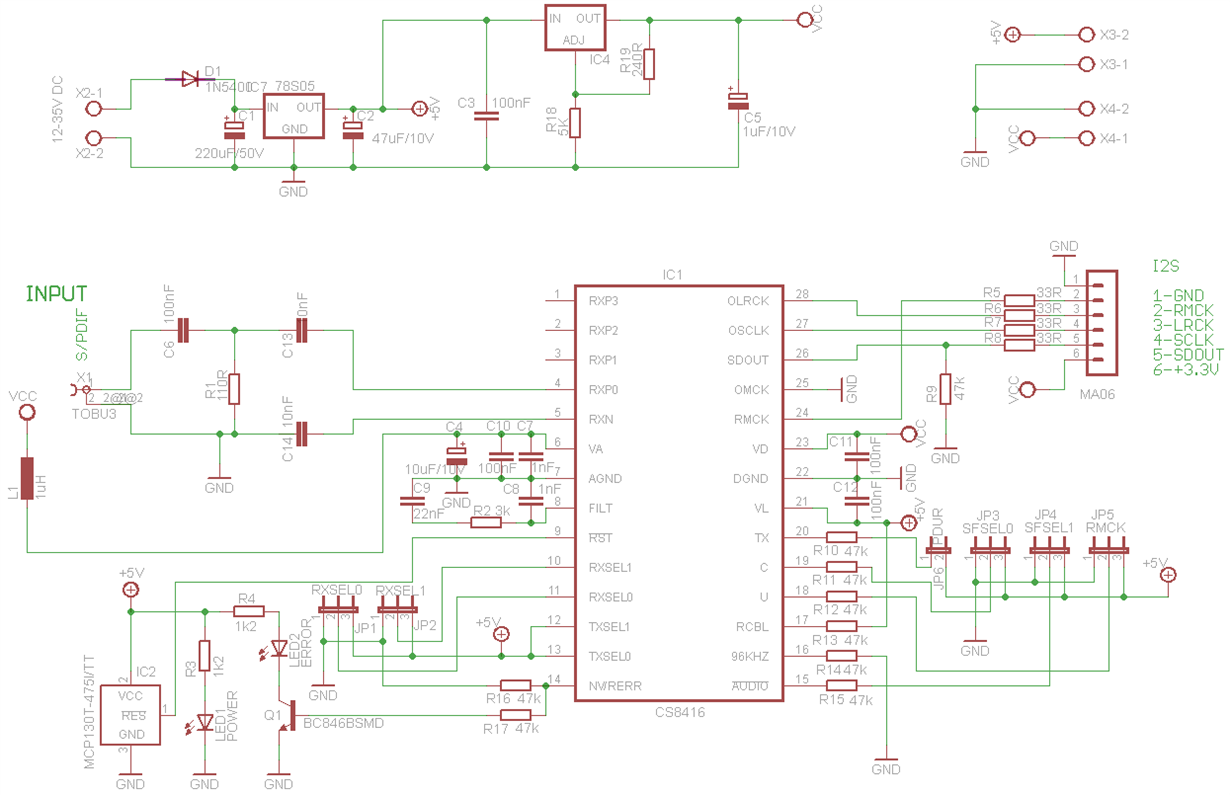

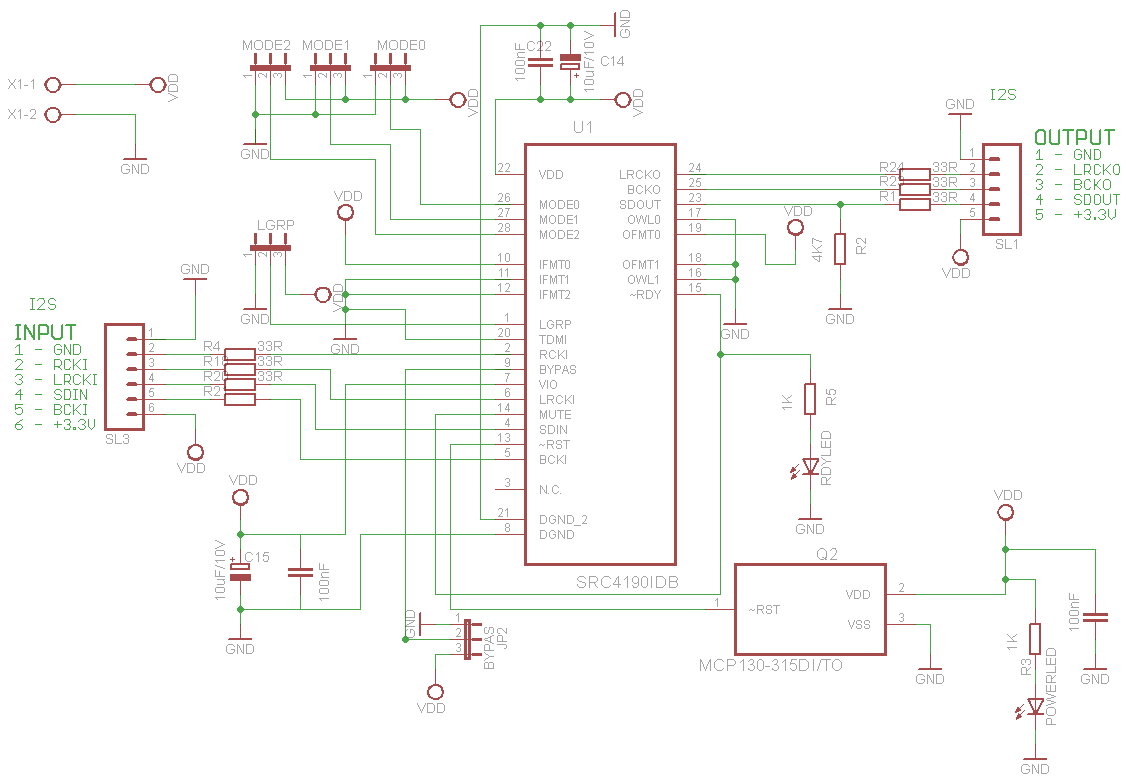

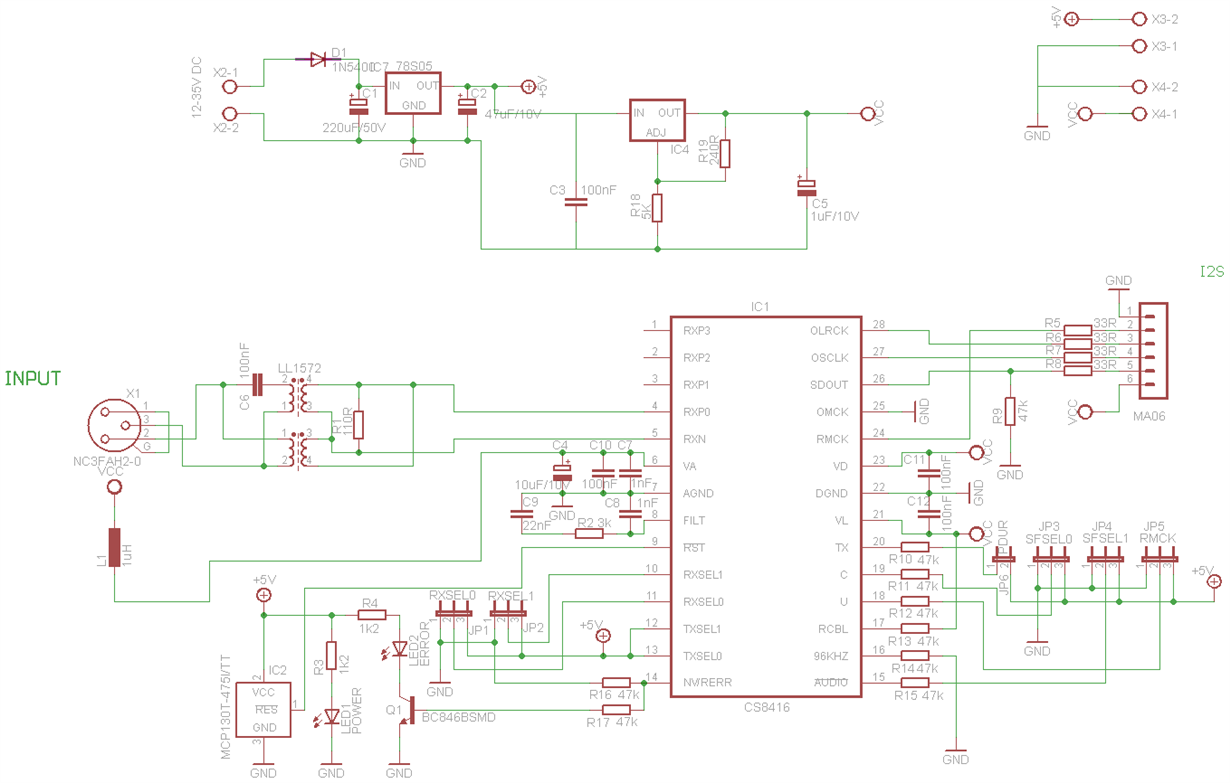

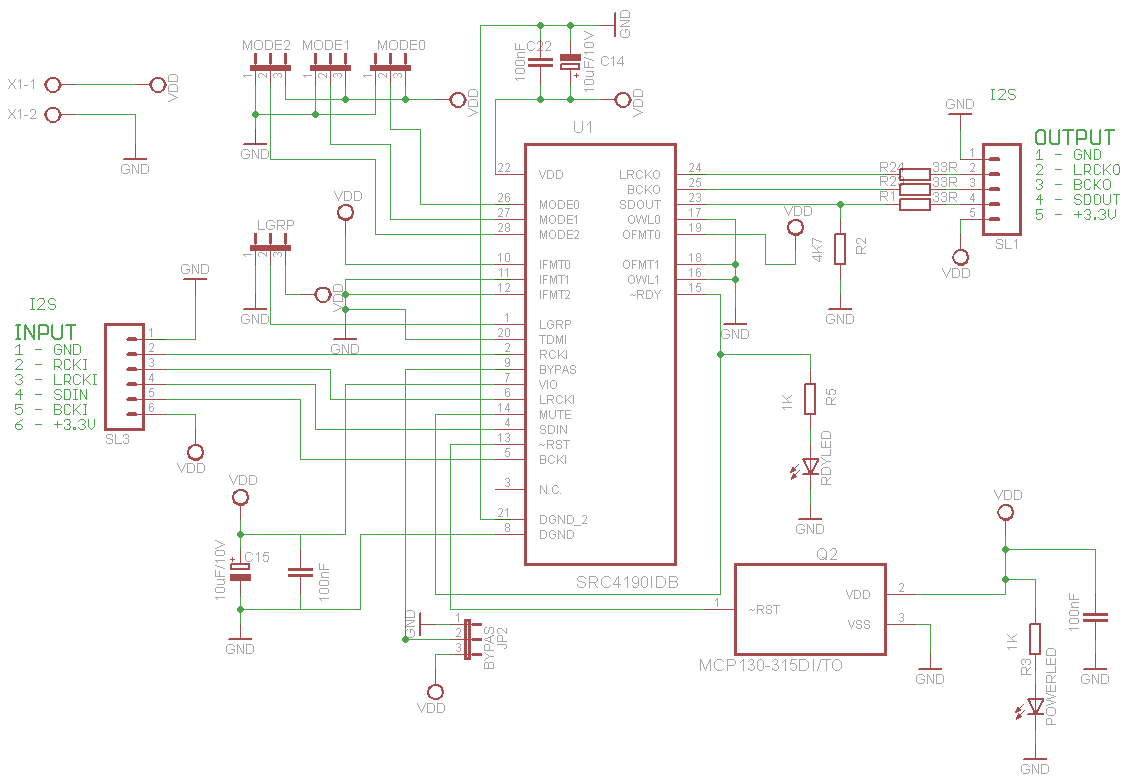

I have made a schematic for SRC4190 which I want to use with the CS8416 to keep the sampling frequency at constant 192KHZ. I have attached here the schematic. I am using the clock form the I2S bus of the the CS8416. I am using the Slave Mode for both input and output, With input Data Format being 24 Bits I2S from Digital Audio Receiver CS8416.

I would appreciate if you can check the schematic and give me some feedback.