I would like to confirm clock setting of TLV320DAC3100.

Our customer uses TLV320DAC3100 as I2C slave and WCLK/BCLK are input.

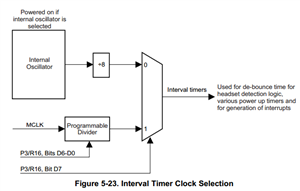

1. How should they set MCLK frequency? Are there any provisions?

Or can they set any frequencys <50MHz?

If if is OK for < 50MHz, should they set 1MHz < the frequency <50MHz for delay timer?

2. For on-chip PLL, can they use on-chip PLL by only setting "1"" for D7 of Page 0 / Register 11 (0x0B): DAC NDAC_VAL without MCLK?

3. If they can 2., can they set "1" of D7 by I2C without MCLK? Or do they need MCLK?

Best regards,

Atsushi Yamauchi